İçindekiler:

- Adım 1: Blok Şeması

- Adım 2: Çalışma Prensibi

- 3. Adım: Mantık Uygulaması

- Adım 4: Kilitlenmeyi Çözme

- Adım 5: Cihaz Yapılandırması - Matrix0 Devresi

- Adım 6: Cihaz Yapılandırması - SPI Saatleme Mantığı

- Adım 7: Cihaz Yapılandırması - Matrix0 Bileşenleri Özellikleri

- Adım 8: Cihaz Yapılandırması - Matrix1 Devresi

- Adım 9: Cihaz Yapılandırması - 3-bit İkili Sayaç

- Adım 10: Cihaz Yapılandırması - 3-bit Karşılaştırma Mantığı

- Adım 11: Cihaz Yapılandırması - Dijital Karşılaştırma Mantığı ve Geçici Kayıt

- Adım 12: Cihaz Yapılandırması - Matrix1 Bileşenleri Özellikleri

- Adım 13: Sonuçlar

- Yazar John Day day@howwhatproduce.com.

- Public 2024-01-30 13:17.

- Son düzenleme 2025-01-23 15:13.

Kontrol sistemleri ve ilgili cihazlar, öngerilim hatları veya piller gibi birden fazla güç kaynağıyla ilgilenir ve belirli bir küme içindeki en yüksek (veya en düşük) hattı izlemelidir.

Örneğin, "çoklu akü" ile çalışan bir sistemde yük değiştirme, sistemin akü dizisi arasındaki minimum veya maksimum voltajı (belirli anahtarlama algoritmasının bir fonksiyonu olarak maks veya min) izlemesini ve yükü dinamik olarak yönlendirmesini gerektirir. gerçek zamanlı olarak en uygun kaynak. Alternatif olarak, uygun şarj için sistemin en düşük voltajlı pilin bağlantısını geçici olarak kesmesi gerekebilir.

Diğer bir örnek, her güneş panelinin bir tiltrote mekanizması ve bir güneş izleme devresi (ikincisi paneli yönlendirmek için Güneş konum bilgisini sağlar) ile donatıldığı modern güneş enerjisi sistemidir. Maksimum voltaj bilgisi ile, her bir güneş paneli konumu, aslında en yüksek çıkış voltajını sağlayan dizinin paneli temelinde ince ayar yapılabilir, böylece üstün bir güç optimizasyonu seviyesi elde edilir.

Prensipte bir maksimum voltaj takipçisi uygulayabilen birkaç farklı ticari IC (esas olarak mikro denetleyiciler) markası vardır. Ancak, programlama gerektirirler ve karma sinyal çözümünden daha az maliyetlidirler. Bir Dialog GreenPAKTM tasarımının eklenmesi, tasarımın satın alınabilirliğini, boyutunu ve modülerliğini olumlu yönde etkileyebilir. Bu tasarım, hem analog hem de dijital devreyi tek bir çipe entegre etmenin avantajından yararlanır.

Bu Eğitilebilir Tabloda, sekiz farklı kaynak arasında bir maksimum (veya nihayetinde minimum) voltaj bulucu uygulamak için gereken analog ön uç ve dijital mantık uygulanmaktadır.

8 kanallı analog maks/min voltaj monitörünü uygulamak için bir SLG46620G kullanılır.

Aşağıda, çözümün 8 kanallı analog maks/min voltaj monitörü oluşturmak için nasıl programlandığını anlamak için gereken adımları açıkladık. Ancak, sadece programlamanın sonucunu almak istiyorsanız, halihazırda tamamlanmış GreenPAK Tasarım Dosyasını görüntülemek için GreenPAK yazılımını indirin. GreenPAK Geliştirme Kitini bilgisayarınıza takın ve 8 kanallı analog maks/min voltaj monitörünü oluşturmak için programa basın.

Adım 1: Blok Şeması

Şekil 1, uygulanan sistemin global diyagramını göstermektedir.

8 adede kadar değişken voltaj kaynağından oluşan bir dizi çoğullanır ve diğerlerine göre en yüksek voltajlı kaynağı seçebilen özelleştirilmiş bir dahili tasarıma bağlı GreenPAK'ın ADC modülüne arayüzlenir. Dahili mantık, bu bilgiyi görüntüleme veya daha fazla işleme için verir.

Tasarım, uygulama için gerekli tüm analog ve dijital yapı taşlarını içerdiğinden GreenPAK SLG46620G ürününü temel alır. Bu uygulamada dizi, GreenPAK IC tarafından doğrudan çalıştırılan bir ADG508 analog çoklayıcı vasıtasıyla taranır.

Çıkış bilgisi, maksimum voltajdaki voltaj kaynağı numarasına karşılık gelen 3 bitlik bir dijital sayıdır. Bu bilgiyi almanın doğrudan bir yolu, numarayı 7 parçalı bir ekran aracılığıyla göstermektir. SLG46620G'nin dijital çıkışını, Referans'ta açıklanan GreenPAK çözümü gibi 7 segmentli bir ekran sürücüsüne veya ortak bir 74LS47 IC'ye bağlayarak kolayca gerçekleştirilebilir.

Sunulan devre maksimum voltajı arar. Tasarımı bir minimum voltaj bulucuya dönüştürmek için, analog çoklayıcı ile GreenPAK analog girişi arasına, çoklayıcı çıkışını 1 V referans voltajından çıkararak basit bir ön koşullandırma devresi eklenmelidir.

Adım 2: Çalışma Prensibi

Tasarım, maksimum voltajlı kaynağı seçmeyi amaçlamaktadır, bu nedenle, son maksimum değeri depolarken ve girişteki bir sonraki değerle (taramadaki bir sonraki voltaj kaynağına ait olan) karşılaştırırken tüm dizi üzerinde bir tarama gerçekleştirilir.

Aşağıda tüm girişler boyunca bir "tarama" veya "döngü" olarak tam bir çoğullama dizisine atıfta bulunacağız.

İki değer arasındaki karşılaştırma, ACMP bileşenleri aracılığıyla değil (ancak, SLG46620G'de mevcuttur), değerler sırasıyla sayısallaştırıldıktan sonra DCMP modülü ile yapılır. Bu, ilk olarak Referans'ta ele alınan gelişmiş ve rafine bir tekniktir.

Şekil 2, SLG46620G'nin bu tasarım için nasıl yapılandırıldığını gösterir.

Analog giriş sinyali, 1'lik bir Kazanç seti ile PGA bileşeni üzerinden ADC girişine gider. GreenPAK ADC modülünün aralığı.

ADC, tek uçlu modda çalışır ve analog sinyali, daha sonra DCMP modülüne aktarılan 8 bitlik bir dijital koda dönüştürür. Dijital kod ayrıca, bir dijital kodun saklanabileceği ve bir sonraki darbe SPI CLK girişine gelene kadar değişmeyeceği bir ADC/FSM Tamponu olarak yapılandırılmış SPI bloğuna beslenir. Özel bir mantık bloğunun SPI CLK girişini çalıştırdığına dikkat edin. Bu kısmı daha sonra inceleyeceğiz, çünkü bu, düzgün işlemden sorumlu olan "temel" mantıktır. Yeni bir dijital kod, yalnızca gerçek maksimum giriş voltajına aitse SPI modülüne kaydedilir.

DCMP bileşeni, mevcut ADC verilerini SPI bloğunda depolanan son kazananla (yani bulunan son maksimum değer) karşılaştırmak için kullanılır. Yeni ADC verisi öncekinden daha büyük olduğunda OUT+ çıkışında bir darbe üretecektir. SPI bloğunu yeni kazananla güncellemek için OUT+ sinyalini kullanıyoruz.

Küresel bir saat sinyali, ADC dönüşümlerini ve genel zamanlamaları yönlendirir. Bir dönüştürme gerçekleştirildikten sonra, ADC'nin INT çıkış sinyali darbeleri, ADC paralel veri çıkışı ile zaman içinde koordine edilir. INT çıkışını ayrıca Matrix1'de DFF'ler tarafından uygulanan 3 bitlik bir ikili sayacı artırmak için kullanırız ve bu üç nedenden dolayı faydalıdır:

1. Sayaç çıkış hatları, harici analog çoklayıcıyı adresler, böylece ADC'ye bir sonraki giriş voltajına hizmet eder;

2. Sayım, bir tarama sırasında geçici kazananı saklamak için 3 bitlik bir kayıtta (Matrix1'de uygulanmıştır) dondurulur;

3. Tarama tamamlandıktan sonra ikinci bir 3 bitlik kaydı (Matrix0'da uygulanır) güncellemek için sayının kodu çözülür.

3. Adım: Mantık Uygulaması

ADC modülü sıralı olarak tüm giriş gerilimlerinin dönüştürülmüş verilerini birbiri ardına süresiz olarak sağlar. Çoklayıcı 0b111'e (ondalık 7) adreslendiğinde, sayaç 0b000'e (ondalık 0) döner ve böylece giriş voltajlarında yeni bir tarama başlatılır.

Tarama sırasında, paralel veri çıkışı geçerli olduğunda ADC INT çıkış sinyali üretilir. Bu sinyal darbe aldığında, analog çoklayıcı PGA'ya karşılık gelen voltajı sağlayarak bir sonraki girişe geçmelidir. Bu nedenle, ADC INT çıkışı, 3 bit paralel çıkış word'ü doğrudan harici analog çoklayıcıya hitap eden Şekil 2'deki 3 bitlik İkili Sayacın doğrudan saatleme sinyalidir (Şekil 1'de “V seçimi”).

Şimdi giriş voltajlarının aşağıdaki ilişkilere sahip olması gereken bir örneğe bakalım:

a) V0 < V1 < V2

b) V2 > V3, V4

c) V5 > V2

Şekil 3, maksimum karar mekanizmasında yer alan ana sinyalleri temsil etmektedir.

Veriler nihayetinde INT darbeleri ile eşzamanlı olarak SPI arabellek kaydına saatlendiğinden, SPI arabellek içeriğinin bir sonraki ADC dönüştürme sonucu ile karşılaştırıldığı bir karşılaştırma penceresi mevcuttur. Bu özel zamanlama, DCMP çıkışında OUT+ darbelerinin üretilmesiyle sonuçlanır. SPI arabellek kaydına yeni değerler yüklemek için bu darbelerden yararlanabiliriz.

Önceki Şekildeki SPI arabellek veri satırından da anlaşılacağı gibi, SPI kaydı her zaman 8 giriş arasındaki en büyük değeri içerir ve yalnızca DCMP modülü tarafından daha büyük bir değer algılandığında güncellenir (DCMP'ye atıfta bulunur). ÇIKIŞ+ grafiğin çıkış hattı, eksik darbeler V2'nin V5 ile karşılaştırılana kadar kayıtta kilitli kalmasına neden olur.

Adım 4: Kilitlenmeyi Çözme

Uygulanan mantık yukarıda açıklandığı gibi olsaydı, bir kilitlenme durumuna çarpacağımız açıktır: sistem sadece SPI tampon kaydında depolanana karşılık gelen voltajdan daha yüksek voltajları tespit edebilir.

Bu, bu voltajın azalması ve daha sonra şimdiye kadar bundan daha düşük olan başka bir girişin en yüksek olması durumunda da geçerlidir: asla algılanmayacaktır. Bu durum, sadece 3 giriş voltajının mevcut olduğu Şekil 4'te daha iyi açıklanmıştır. açıklık.

2. yineleme sırasında V3 düşer ve V1 gerçek maksimum voltajdır. Ancak DCMP modülü bir darbe sağlamaz çünkü SPI arabellek kaydında saklanan veriler (0,6 V'a karşılık gelir) V1'e (0,4 V) karşılık gelenden daha büyüktür.

Sistem daha sonra "mutlak" bir maksimum bulucu gibi davranır ve çıktıyı doğru şekilde güncellemez.

Bu sorunun üstesinden gelmenin güzel bir yolu, sistem tüm kanalların tam bir yoklama döngüsünü tamamladığında verileri SPI Tampon Kaydı'na yeniden yüklemeye zorlamaktır.

Aslında, o girişteki voltaj hala en yüksekse, hiçbir şey değişmez ve kontrol güvenli bir şekilde devam eder (yukarıdaki Şekil 4'e bakın, bu, Döngü Yinelemeleri 0 ve 1'in durumudur). Öte yandan, bu girişteki voltaj şans eseri başka bir girişten daha düşük bir değere düşerse, değeri yeniden yüklemek DCMP modülüne yeni maksimum değerle karşılaştırırken bir ÇIKIŞ+ darbesi üretme olanağı verir (bu, Döngü Yinelemeleri 2 ve 3) durumu.

Problemin üstesinden gelmek için bir parça mantık devresi gereklidir. Döngü gerçek maksimum girişe ulaştığında SPI bileşenine bir saat sinyali üretmeli, böylece güncellenmiş veri kelimesinin SPI Tampon Kaydı'na yeniden yüklenmesini sağlamalıdır. Bu, aşağıdaki Bölüm 7.2 ve 7.6'da tartışılacaktır.

Adım 5: Cihaz Yapılandırması - Matrix0 Devresi

SLG46620G, Şekil 2'de gösterildiği gibi iki Matrix bloğuna sahiptir. Aşağıdaki Şekiller ilgili cihaz konfigürasyonlarını göstermektedir.

Devrenin üst kısmı 3 DFF (DFF0, DFF1 ve DFF2) ile gerçekleştirilen “Loop Register”dır. Giriş çoklayıcının her döngüsünden sonra, 7-segment ekran sürücüsüne “kazanan”ın ikili numarasını, yani son taramada en yüksek voltajlı girişi göndermek için yenilenir. Hem DFF'lere giden saat hem de veriler, sırasıyla P12, P13, P14 ve P15 bağlantı noktası aracılığıyla Matrix1'de uygulanan mantıktan gelir.

Alt kısım, Pin 8'de giriş ve x1 kazançlı PGA ile analog ön uçtur. ADC INT çıkışı hem SPI'nin saat mantığına hem de uygulanan sayaç için saat sinyali olarak hizmet edeceği P0 portu üzerinden Matrix1'e gider.

ADC ve SPI paralel veri çıkışları, Matrix1'de DCMP bileşenine bağlanacak şekilde sırasıyla NET11 ve NET15 olarak etiketlenir.

Adım 6: Cihaz Yapılandırması - SPI Saatleme Mantığı

Daha önce “Mantık Uygulaması” bölümünde belirtildiği gibi, SPI Tampon Kaydı, gerçek saklanan değer ile yeni ADC dönüştürme verileri arasındaki bir karşılaştırmanın DCMP OUT+ çıkışında bir darbe oluşturduğu her seferinde güncellenir.

Bu sinyal ADC INT çıkışı ile AND-ed ise sinyal bütünlüğü sağlanır. Bu, herhangi bir ani ve yanlış tetiklemeyi önler.

Ayrıca kilitlenme durumlarını atlamak için döngü gerçek kazanan verisine ulaştığında SPI Tamponunun güncellenmesi gerektiğinin de altını çizmiştik.

Daha sonra uygun SPI saat ölçümü için oyunda üç sinyal vardır:

1. ADC INT çıkışı (LUT0-IN1)

2. DCMP OUT+ çıkışı (P10 portu üzerinden LUT0-IN0)

3. Sayı, Kilitleme sinyaline eşittir (P11 portu üzerinden LUT0-IN2)

İlk ikisi AND-ed ve her ikisi de LUT0'da ikincisi ile OR-ed'dir ve uygulaması Şekil 6'daki gibi yapılandırılmıştır.

Adım 7: Cihaz Yapılandırması - Matrix0 Bileşenleri Özellikleri

Şekil 7-10, Matrix0'a ait kalan bileşen özellik pencerelerini göstermektedir.

Adım 8: Cihaz Yapılandırması - Matrix1 Devresi

Adım 9: Cihaz Yapılandırması - 3-bit İkili Sayaç

Devrenin üst kısmı, daha önce tartışıldığı gibi, esas olarak ADC INT çıkışı tarafından saatlenen 3 bitlik bir ikili sayaç olan mantık öğelerini içerir. Bu sayaç, Şekil 12'de gösterilen oldukça “standart” bir şematik ile uygulanmaktadır.

Bu sayaç tasarımımızda Flip-Flop'lar DFF9, DFF10, DFF11 ve INV1, LUT4, LUT8 aracılığıyla gerçekleştirilmektedir. Şekil 13'te gösterildiği gibi DFF9 çıkışı LSB iken DFF11 MSB'dir.

LUT4, bir XOR olarak yapılandırılırken LUT8, Şekil 12'deki AND-XOR mantığını gerçekleştirir.

Sayaç çıkışları, harici Analog Multiplexer'ı adreslemek için üç dijital çıkış pinine gider.

LUT10, bir tarama tamamlandığında sayacın kodunu çözer ve DLY8 ve P12 portu aracılığıyla Matrix0'a bir darbe besler. Bu, sayacın çıkışlarını AND-ing yaparak ve böylece 7 dec sayısını (0b111 ikili, döngü sonu) çözerek gerçekleştirilir.

Adım 10: Cihaz Yapılandırması - 3-bit Karşılaştırma Mantığı

Şekil 15, döngünün geçerli "kazanan" adreste yinelendiğini algılamak için kullanılan devreyi göstermektedir. Bu durumda, daha önce tartışıldığı gibi, olası bir kilitlenme durumunu çözmek için bir dijital darbe mevcut ADC sonucunun yeniden yüklenmesini sağlamalıdır.

"Kazanan" adres, Matrix1'in geçici kaydında saklanır (aşağıya bakın), mevcut adres ise ikili sayaç tarafından çıkarılır.

XNOR kapıları, her iki giriş de eşit olduğunda gerçek (mantık 1 veya 'yüksek') bir çıkış sağlar. Bu sinyali tüm bitler için VE-ing (LUT9), her iki ikili kod aynı olduğunda bize bir darbe verir. Bir eşlik denetleyicisi olarak XOR kapıları hakkında ayrıntılar Referans'ta bulunabilir.

"Karşı-eşittir-Mandal" sinyali, P11 bağlantı noktası aracılığıyla Matrix0'a iletilir.

Adım 11: Cihaz Yapılandırması - Dijital Karşılaştırma Mantığı ve Geçici Kayıt

Şekil 11'in alt kısmı (Şekil 16'da vurgulanmıştır), bu tasarımın karar verme kısmı olan DCMP bloğunu göstermektedir.

DFF6, 7 ve 8, döngü çalışırken "kazanan" geçici giriş numarasını depolamak için 3 bitlik bir kayıt oluşturur. Flip-Flop'lara giriş, Şekil 11'deki global Matrix1 devresinde görüldüğü gibi 3 bitlik ikili sayaç çıkışlarıdır ve burada açıklık amacıyla atlanmıştır.

Burada saklanan değer bir tarama sırasında değiştiğinden ve yalnızca taramanın sonunda "geçerli" olarak kabul edildiğinden, bu kaydın çıktıları doğrudan 7 segmentli ekranı çalıştıramaz.

Bu nedenle, geçici kayıt çıkışları, matrisler arası P13, P14 ve P15 bağlantı noktaları aracılığıyla Matrix0'ın Döngü Kaydı'na bağlanır.

Şekil 16'da, ADC-SPI kayıtları karşılaştırma sonuçlarını yeni bir maksimumda bulduğunda, geçici kaydın DCMP OUT+ çıkışı tarafından saatlendiğini gözlemlemek önemlidir.

Aynı OUT+ sinyali, P10 portu üzerinden Matrix0, SPI CLK Logic'e iletilir.

Adım 12: Cihaz Yapılandırması - Matrix1 Bileşenleri Özellikleri

Şekil 17-19, Matrix1'e ait bileşen özellik pencerelerini göstermektedir.

Adım 13: Sonuçlar

Uygulamayı test etmek için, 8 analog giriş voltajının TrimPot'lu bir dizi direnç bölücü tarafından elde edildiği bir değerlendirme panosu prototipi oluşturulmuştur (Şekil 20'de gösterildiği gibi).

Kullanılan çoklayıcı, tek besleme (12 V) ile çalışabilen bir ADG508 parçasıdır.

7 segmentli ekran sürücüsü bir 74LS47'dir. Paralel bir giriş kelimesinin kodunu çözer ve doğrudan ortak anot 7 segmentli bir ekranı çalıştırır.

Değerlendirme panosu, Şekil 21'de gösterildiği gibi genişleme konektöründe doğrudan GreenPAK Gelişmiş Geliştirme Platformuna takmak için 2x10 dik açılı konektöre sahiptir.

GreenPAK Gelişmiş Geliştirme Platformu ile bağlantı, hızlı bir kontrol için sinyallerin ölçümlerini almayı çok basit hale getirir. Örneğin, Şekil 22, bir HP 54620A Mantık Analizörü tarafından yakalanan bir dizi sinyali (sırasıyla SAAT, ADC INT çıkışı ve DCMP OUT+ çıkışı) göstermektedir. Dalga biçimleri, OUT+ sinyalinin yükselen kenarı tarafından tetiklenir ('A>B' olarak etiketlenen kapsamda), dolayısıyla bu, analog girişler arasında yeni bir maksimum Voltaj algılandığında bir dalga biçimi yakalamadır. Aslında, Şekil 22'de gösterilen ilgili voltajı artırmak için Değerlendirme Kurulunun TrimPot'larından birinin döndürülmesiyle elde edilmiştir.

Şekil 23, Değerlendirme Kurulu'nun şemasını göstermektedir.

Çözüm

Bu Eğitilebilir Tabloda, çok kanallı kontrol sistemlerine ortak bir ek olarak kullanılmak üzere sekiz kanallı bir maksimum (veya minimum) voltaj bulucu uyguladık. Sunulan yaklaşım, GreenPAK bileşenlerinin gelişmiş özelliklerinden yararlanır ve tek bir çip analog ve dijital işlevlere entegre etmenin nasıl mümkün olduğunu gösterir. Uygulama boyutunun ve maliyetinin azaltılabilmesi için birkaç ticari IC, Dialog GreenPAK'lerle değiştirilebilir.

Önerilen:

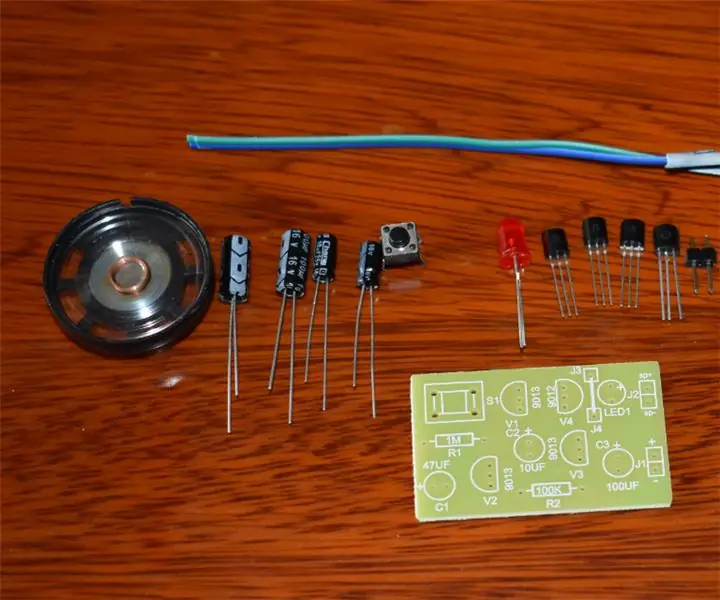

Analog Devre Bilgisi - IC'siz Bir Tikleyen Saat Ses Efekti Devresi Kendin Yap: 7 Adım (Resimlerle)

Analog Devre Bilgisi - IC'siz Bir Tikleyen Saat Ses Efekti Devresi Kendin Yap: Bu tıkırtılı Saat Ses Efekti Devresi, herhangi bir IC bileşeni içermeyen sadece transistörler, dirençler ve kapasitörler ile inşa edilmiştir. Bu pratik ve basit devre ile temel devre bilgilerini öğrenmeniz sizin için idealdir.Gerekli mat

Yüksek Gerilim Aküler için Gerilim Monitörü: 3 Adım (Resimlerle)

Yüksek Voltajlı Piller için Voltaj Monitörü: Bu kılavuzda size elektrikli longboard'um için akü voltaj monitörümü nasıl kurduğumu açıklayacağım. İstediğiniz şekilde monte edin ve pilinize sadece iki kablo bağlayın (Gnd ve Vcc). Bu kılavuz, pil voltajınızın 30 volt'u aştığını varsaymıştır, w

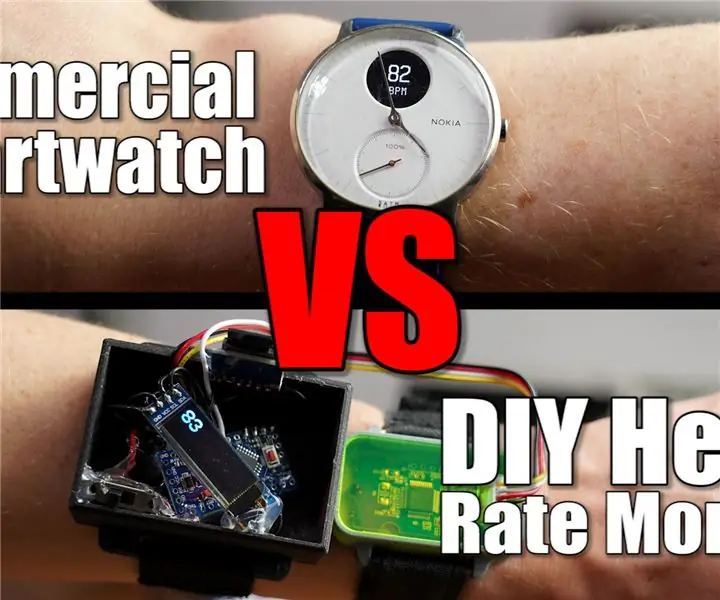

Kendin Yap Nabız Monitörü (kayıt cihazı): 4 Adım

DIY Kalp Atış Hızı Monitörü (logger): Bu projede size ticari bir akıllı saatin kalp atış hızınızı nasıl ölçtüğünü ve izlediğini göstereceğim ve ardından, temelde aynı şeyi yapabilen bir DIY devresinin nasıl oluşturulacağını göstereceğim. kalp atış hızı verilerini saklayın

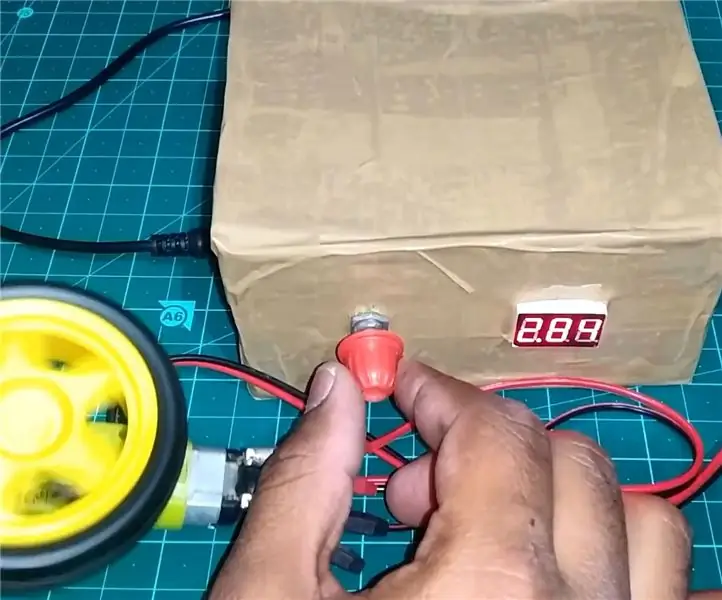

LM317 Kullanan Kendin Yap Güç Kaynağı - Lm 317 Değişken Gerilim Çıkışı: 12 Adım

LM317 Kullanan Kendin Yap Güç Kaynağı | Lm 317 Değişken Gerilim Çıkışı: Bugün küçük projeleriniz için küçük bir güç kaynağı ünitesinin nasıl yapıldığını öğreneceğiz.LM317, düşük akım güç kaynağı için iyi bir seçim olacaktır.Lm317, gerçekte bağlı olan direncin değerine bağlı olarak değişken çıkış voltajı sağlar.

WiFi Uyarıları ile Mini Kendin Yap Hidroponik Sistemler ve Kendin Yap Hidroponik Bitki Bahçesi İnşa Et: 18 Adım

WiFi Uyarıları ile bir Mini Kendin Yap Hidroponik Sistemler ve Kendin Yap Hidroponik Bitki Bahçesi İnşa Et: Bu derste size bir #Kendin Yap #hidroponik sistemini nasıl kuracağınızı göstereceğiz. Bu DIY hidroponik sistem, 2 dakika açık ve 4 dakika kapalı olan özel bir hidroponik sulama döngüsünde sulayacaktır. Ayrıca rezervuar su seviyesini de izleyecektir. Bu sistem