İçindekiler:

- Yazar John Day day@howwhatproduce.com.

- Public 2024-01-30 13:16.

- Son düzenleme 2025-01-23 15:13.

Geçmişte, Z80 tabanlı bir bilgisayarın nasıl kurulacağına dair bir kılavuz yazdım ve devreyi olabildiğince basit olacak şekilde tasarladım, böylece mümkün olduğunca kolay kurulabilirdi. Ben de aynı basitlik fikrini kullanarak küçük bir program yazdım. Bu tasarım oldukça iyi çalıştı, ancak bundan tamamen memnun değildim. Çalışma zamanı sırasında programlanmasına izin veren bir programı yeniden yazmaya başladım. Bu, kod parçalarını EEPROM'a adamak zorunda kalmadan test etmeme izin veriyordu, bu da EEPROM'u yeniden programlamamı gerektiriyordu. Bu bana eğlenceli bir fikir gibi gelmedi. Sonra hafıza alanları hakkında düşünmeye başladım. Bir donanım parçasını (esas olarak IO) arayüzlemek istersem, bir kod parçası, sistem için mevcut olan bellek alanını potansiyel olarak aşabilir. Tasarımın yalnızca adres yolunun alt baytını kullandığını ve ardından yüksek baytın alt bitinin ROM ve RAM alanları arasında seçim yapmak için kullanıldığını unutmayın. Bu, kullanmak için yalnızca 253 bayt alanım olduğu anlamına geliyordu. Neden 256 yerine 253 diye soruyor olabilirsiniz. Bunun nedeni, yeni kodumun yazılı bir programın sonunda üç bayt veri enjekte etmesidir (bu, yeni tasarım üzerinde çalışmak için değiştirdiğim için daha sonra ele alınacaktır).

n

Başka neler olup bittiğini görmek için eski şemalarıma geri döndüm. Oraya vardığımda kapatacağım bellek seçim devresinde küçük bir kusur buldum. Basitleştirilmiş versiyon: Her zaman RAM'e konmasına rağmen, tüm yazma istekleri gerçekten geçerdi. Bu muhtemelen endişelenmeye değecek bir şey değildi ama bu sefer düzgün bir şekilde yapmak istedim. Ve bununla birlikte yeni bir şema çizmeye başladım. Bu sayfaya eklenen iki resim, gerçek devrenin öncesi ve sonrasıdır. Spagetti kablolarının çoğunu temizledim, komik değil.

n

Orijinal gönderimi takip ettiyseniz ve bununla birlikte takip etmeyi planlıyorsanız, benden nefret edeceksiniz. Yeni başlıyorsanız, şanslısınız demektir. Listedeki parçaları (veya eşdeğerlerini) alın ve takip edin.

Gereçler:

LM7805 - 5 Volt regülatörZ80 - CPU; AT28C64B - EEPROM sisteminin beyinleri. Bilgisayarın donanım yazılımıIDT6116SA - SRAM için kullanılan “kalıcı” veri depolama; kullanıcı kodu ve/veya genel veri depolama için kullanılırNE555 - Sistem saati74HC374 - /OE ile Sekizli D-Latch; giriş çipi olarak kullanılır74LS273 - /MR ile Sekizli D-Latch; çıkış yongasıTLC59211 - LED sürücü yongası (74LS273'ün LED'leri sürmesi için kullanılır, çünkü tek başına mevcut çıkışa sahip değildir)MC14572 - Bu bir "Hat Sürücüsü" yongasıdır, ancak bunu Bellek Kontrolü mantığı için mükemmel buldum. 4 invertöre ve yerleşik bir NAND ve NOR geçidine sahiptir74LS32 - Quad OR gateCD4001 - Quad NOR gateCD4040 - 12 Aşamalı Dalgalanma Sayacı; Çizilmiş, ancak uygulanmamış saat bölücü (sistemi daha düşük saat hızlarında çalıştırmak için)2 10K Ohm Dirençler - Biri 555 zamanlayıcı devresinde kullanılır, bu yüzden onun için istediğiniz değeri kullanın4 1K Ohm Dirençler - Biri için kullanılır 555 zamanlayıcı devresi, onun için ne istersen onu kullan. Bir diğeri LED'leri sürmek için kullanılır, bu nedenle 8x330 Ohm Direnç Veriyolu8x10K Ohm Direnç Veriyolu11 LED'leri - Üçü sistem durumu için kullanılır ve diğer sekizi çıkışlardır. 8 için bir çubuk grafik ekran kullandım (HDSP-4836)4 Kapasitörler - LM7805'te iki adet kullanılır; 0.22uF ve 0.1uF. Biri 555 zamanlayıcı içindir, bu yüzden doğru olduğunu düşündüğünüzü kullanın. Sonuncusu, açılışta sıfırlama içindir; 100uF2 N. O. Basmalı Butonlar - Biri giriş için, diğeri reset için kullanılır8 SPST DIP Anahtarları - Veri girişi; Piano Key styleWire kullandım. Çok ve çok tel

n

NOT: MC14572 açık delik sürümü eskidir, ancak SMD sürümü hala etkindir ("yeni tasarım için değil" durumu bile değildir), bu nedenle kullanmanıza izin vermek için bir devre kartı satın almanız gerekebilir. MC14572'nin yerine ikinci bir 74LS32 kullanılabilir (önceki ible "bellek seçim devresi" şemasına bakın)

Adım 1: Değişikliklere + Şemalara Hızlı Genel Bakış

Şemalar nasıl okunur: Bir çipe doğrultulmuş bir ok bir giriştir:Giriş >-Çipten uzağa bakan bir ok bir çıkıştır:Çıkış <-Bus'lar ok yerine bir çizgi kullanır:Bus |-

n

Çiplerin çoğu, tam pin çıkışlarıyla çizilmiştir. Bu çipler üzerinde küçük bir dip çizildi. Çoğu çipin üzerinde pin numaraları ve etiketler de bulunur. Okumaları biraz zor olabilir. Kalemim köreliyordu.

n

Devre bağlantıları açısından, yeni tasarımın düzeni orijinalinden büyük ölçüde değişmemiştir. Adres yüksek baytının alt bitini belleklere bağladım ve ardından RAM/ROM seçimi için üst baytın (A12) düşük bitini kullandım. Bu, ROM alanının 0000-00FF'den 0000-0FFF'ye çıktığı anlamına geliyordu. Ram alanı 0100-01FF'den 1000-1FFF'ye gitti. Ayrıca daha iyi bir tasarım için Bellek Kontrolü mantığını değiştirdim ve iki yeni durum LED'i (ve bir miktar yapıştırıcı mantığı) ekledim. Ayrıca bir saat bölücü devre çizdim (ama kablolama yapmadım). İki işlevi yerine getirmekti. Açık olan işlev, saat frekansını aşağı bölmektir. Diğer işlev PWM (Darbe Genişliği Modülasyonu) amaçları içindir, çünkü 555 %50 görev döngülü dalgalar üretmez. Bu devrede bu gerçekten önemli değil, ancak bazı LED'leri sürmek için saati kullanmak isteseydiniz, etkileri kesinlikle fark edeceksiniz (bir (bir dizi) LED(ler) diğerinden daha sönük olacaktır). Devrenin geri kalanının tamamı esasen değişmemiştir.

Adım 2: CPU, Bellek ve Bellek Kontrolü

Bu, önceki versiyonumun okuyucularının benden nefret ettiği kısım. Orijinal yapıda, kablolama ile ilgili küçük bir sorun yaratacak gibi göründükleri bir yere tahtaya parçaları fırlattım. Sonuç, sanki biri üzerine bir tabak spagetti dökmüş ve “teller” gibiydi. Biraz temizlemek istedim, bu yüzden CPU, RAM ve ROM dışındaki her şeyi sökerek başladım. Neredeyse tüm giriş devresini, çıkış devresini ve bağlantı mantığını çıkardım. Bunu yapmak neredeyse canımı yakıyordu ama gerekliydi. Tüm veri bağlantılarını sağlam ve adres yolunun alt baytını bıraktım. Daha sonra adres veriyolunun (A8-A11) sonraki dört bitini ROM çipine bağladım. Yeniden programlama için yukarı çekmeyi kolaylaştırmak için bu sefer çipin etrafından dolaşmaya özen gösterdim. Adres bağlantılarını da RAM çipine atladım.

n

Bunun dışında, şimdi hafıza kontrol mantığını kablolu hale getirmem gerekiyordu. Orijinal şemada, işlemcinin /MREQ hattını doğrudan /CE'ye her iki bellek yongasına bağladım, ardından /WR'yi RAM'in /WE'sine bağladım. Daha sonra CPU'nun /RD ve /MREQ'sini mantıksal olarak VEYA'yı A9'un yanı sıra bir araya getirdim. Esasen, tüm bellek isteklerinin hem RAM'i hem de ROM'u etkinleştireceği şekilde ayarlandı, ancak hangi çiplerin / OE'nin seçildiğini seçmek için A9 kullanıldı. Bu iyiydi ve hepsi bir bellek isteği yapılana kadar çipler etkin olmadığı için ve daha sonra bir okuma isteği sırasında yalnızca bir /OE etkin olacağı için. Bu, karışmayı engelledi, ancak garip bir nüans ortaya çıkardı. A9 yalnızca hangi yonganın veri çıkışı yaptığını belirlemek için kullanıldığından ve CPU'nun RAM'in /WE pinine doğrudan erişimi olduğundan, tüm yazma istekleri geçerdi. Bu, ROM için sorun değildi çünkü yazma modu /WE doğrudan 5V kaynağına bağlanarak engelleniyor. Ancak RAM, A9'dan bağımsız olarak yazılacaktır. Bu, bir ROM alanı konumuna yazma girişiminin RAM alanında aynı konuma yazacağı anlamına geliyordu.

n

Bunun için bir çözüm, CPU'nun çiplerin /OE ve /WE pinlerine doğrudan erişimi olacak şekilde kontrol mantığını yeniden düzenlemek ve ardından hangi çiplerin /CE'nin sürüldüğünü seçmek için MREQ ve A12'yi kullanmak olacaktır. Bu fikirle yola çıktım, ancak orijinal tasarım gibi dört NOR geçidi ve bir invertör kullanmak yerine, bu görev için mükemmel olan garip bir küçük çip buldum. Yalnızca çipte bulunan mantık kapılarını kullanan bir devre oluşturmam gerekiyordu ama bu yeterince kolaydı. A12, doğrudan bir NAND geçidine ve bir NOR geçidine beslenir. /MREQ, NOR kapısına beslenir ve tamamlayıcısı NAND kapısına beslenir. NAND geçidi, RAM için /CE'yi sürmek için kullanılır ve NOR çıkışı ters çevrilir ve ROM/CE'yi sürmek için kullanılır. Bu, her iki çip seçilmeden önce /MREQ'in düşük olmasını ve ardından hangisinin seçileceğini A12'nin seçmesini sağlar. Bu kurulumla, artık ROM'a herhangi bir yazma isteği hiçbir şey yapmayacaktır. Aynı zamanda, her ikisi yerine yalnızca bir çip etkin olduğu için güç tasarrufu sağlar. Mantık çipinin kendisine gelince, içinde hala iki tane kullanılmamış invertör var. Biri daha sonra alışacak, ama oraya vardığımızda oraya varacağız.

Adım 3: Sistem Durumu LED'leri

Bu projeye başlamadan önce, belirli bir IC ile arayüz oluşturmaya çalışıyordum ama bununla ilgili sorun yaşıyordum. Neler olup bittiğinden emin değilim, etrafı araştırmak için panel montajlı bir LED kullandım (yerleşik bir dirence sahip olan tertibatlardan biri). Bunu yapmak bana bugün hala kullanılan bir nostalji fikri verdi: durum LED'leri hafızanın okunup okunmadığını veya hafızaya yazıldığını gösteriyordu. Zaten sahip olduğum giriş LED'i ile birlikte kullanılacaktı. Giriş LED'i, sistemin giriş beklediğini bize göstermek için /WAIT sinyal üretecine bağlandı (oraya geleceğim, merak etmeyin). Bir IO yazısını belirtmek için bir LED eklemeyi düşündüm, ancak değişen çıkış LED'lerinin zaten bunun harika bir göstergesi olacağını düşündüm. Üzerinde düşünüyorum, yine de ekleyebilirim. Yine de, hafızanın okunup okunmadığını bilmeyi faydalı buluyorum. Her neyse, program hata ayıklaması için kullanışlıdır. Aslında programımı çalışır hale getirmeye çalışırken bu şekilde yoğun bir şekilde kullandım: “neden belleğe yazıyor? Henüz bunu yapmaması gerekiyordu!"

n

Bu LED'leri kontrol etmek için dörtlü NOR geçidini kullandım. Tüm kapıları kullandım. Durum sinyallerini oluşturmak için yalnızca ikisi kullanıldı, ancak çipin LED'leri fiilen çalıştıracak güç yetenekleri yok. Bu kadar gücü batırabilirler, bu yüzden diğer iki NOR geçidini invertör olarak kullandım ve LED'leri bu şekilde bağladım. Bir LED okuma, diğeri yazma için kullanıldığından ve aynı anda bir okuma ve yazma isteği oluşmayacağından, her iki LED için de yalnızca bir direnç kullanarak kurtulabildim. Şifresini çözmem gereken sinyallere gelince, bu da yeterince kolaydı. Tüm bellek okuma isteklerinin belirtilmesini istedim, bu nedenle ilk NOR geçidinin girişlerinde /MREQ ve /RD vardı. Yazma durumu biraz daha zordu, ama aynı derecede kolaydı. Yine de bir giriş olarak /MREQ kullandım, ancak /WR'yi diğeri olarak kullanmak, kaçınmak istediğim küçük bir nüansa neden olur. TÜM yazma isteklerini belirtirdi. Ben sadece gerçekten geçenleri istedim. Peki bunu nasıl yapardım? Peki, sadece RAM'in yazılabilmesi için sistemi nasıl kurduğumu hatırlıyor musun? NOR geçidinin diğer girişi olarak RAM'leri /CE'yi kullandım. Bu, LED'in yalnızca RAM seçildiğinde ve bir yazma isteği yapıldığında yanacağı anlamına gelir. LED rengi açısından, okuma göstergesi olarak turuncu (ancak sadece sarı olanları buldum) ve yazma göstergesi olarak kırmızı seçtim.

Adım 4: Giriş ve Çıkış

Önceki adımda, bileşenlerin geri kalanından bazılarını zaten panoya eklediğimi fark etmiş olabilirsiniz. Bir bileşen istediğim yere yanlışlıkla kablo yerleştirmemek için alanı ayırıyordum (böylece söz konusu bileşen için yeni bir yer bulmam gerekecekti). Ayrıca giriş anahtarlarını yerinde bıraktığımı ve güç rayına bağladığımı fark etmiş olabilirsiniz. Orijinal konumun mükemmel nokta olduğuna karar verdim ve çıkış LED'lerini yakına yerleştirmeye karar verdim (yukarıda). Çubuk ekranının sağında giriş mandalı bulunur. Bunun üstünde çıkış mandalı ve solunda LED sürücüsü var. Yapması en kolayı olduğu için ekranı sürücüye bağlayarak başladım. Ardından anahtarları giriş mandalının giriş tarafına bağladım. Daha sonra çıkış mandalının çıkış tarafını LED sürücüsüne bağladım. Bunları kablolamak için garip bir emir gibi görünebilir, ancak bunun bir nedeni vardı. Çıkış mandalının girişi, giriş mandalının çıkışının yanı sıra veri yoluna bağlanacaktı. Fikir, giriş mandalının çıkışlarını, yaptığım çıkış mandalının girişlerine bağlamaktı. O zaman tek yapmam gereken o karışıklığı veri yoluna bağlamaktı. Bu bağlantıların fiziksel olarak nereye gittiği önemli değildi çünkü hepsi elektriksel olarak bağlı olacaktı. Bilgisayar şimdi neredeyse bitti.

Adım 5: Giriş ve Çıkış Sıfırlama ve Bitirme

Üzgünüz, bu adım için resim yok. Resimler için önceki adıma bakın.

n

Bir önceki adımın son resminde fark etmişsinizdir, yeşil bir düğmem vardı ve başka bir mantık yongası takılıydı. Çip, VEYA kapısıdır. /WAIT sinyalini oluşturmak için iki kapı kullanılır. Peki, işlemciden OR-ing /IORQ ve /RD ile sinyal üretilir. Çıktı ikinci kapıya beslenir, burada tekrar bir basma düğmesine VEYA'lanır. Düğme, geçidin girişini yükseğe getirir, böylece çıkışı da yükseğe getirir. Bu çıkış, işlemcilerin /WAIT pinine beslenir. Basılmadığında, bir direnç girişi düşük tutar. Başlangıçta 10K'lık bir direnç kullandım, ancak LS32 aslında girişe voltaj veriyordu. Direnç yeterince düşürmedi ve 1K ile değiştirmek zorunda kaldım. Her neyse, fikir şu ki, bir IO okuma isteği yapıldığında, birinci ve ikinci OR kapıları işlemciye beklemesini söyler. Giriş anahtarlarını istediğiniz şekilde ayarladıktan sonra düğmeye basarsınız ve CPU'yu bekleme durumundan çıkarır. Yeşil “giriş” LED'i, daha önceki bir adımda adlandırdığım gibi, /WAIT pini azaldığında yanacak şekilde kablolanmıştır.

n

Ama henüz işimiz bitmedi. Giriş flip flop, veri girişinin ne zaman geçerli olduğunu ve CPU'ya gönderilmesi gerektiğini bildirmek için bir sinyale ihtiyaç duyar. Bu saat pimi aktif yüksek. Daha önce, onu sadece düğmeye bağladık. Bu hala geçerli bir seçenek, ancak bu sefer onu ikinci VEYA geçidiyle aynı çıktıya koymayı seçtim. Bu IC'nin ayrıca sürülmesi gereken bir /OE pini vardır. Yüksek tutulacak olsaydı, veri yoluna asla veri eklemezdi. Düşük tutulursa, her zaman otobüsü kullanıyor olurdu. Bunu düzeltmek için üçüncü bir VEYA geçidi kullandım. Girişler /IORQ ve /RD'dir ve çıkış doğrudan mandalın /OE'sine gider.

n

Çıkış mandalının da çalıştırılması için saat pimine ihtiyacı vardır. Yine, aktif yüksek. Şemamda, /IORQ ve /WR kullanarak doğrudan pimi süren dördüncü VEYA kapısını çizdim. Bu, bir yazma isteği yapılana kadar saat piminin yüksek tutulacağı, ardından düşük sonra tekrar yüksek olacağı anlamına geliyordu. Bu muhtemelen iyi olurdu, çünkü veri yolu, yazma girişiminden hemen sonra üzerinde hala geçerli verilere sahip olacaktı, ancak mühendislik açısından bakıldığında, çöp bir tasarımdı. Son fotoğrafları çekene kadar bu hatayı fark etmedim, ancak bu bağlantıyı kopardım ve ardından VEYA geçidi çıkışını bellek kontrol mantığından kullanılmayan invertörlerden birine besledim, ardından çıkışını saat pimine bağladım.. Ayrıca şemayı düzelttim ve yaptığım başka bir hata buldum. ben de düzelttim.

n

Sonunda tüm bunlar bittiğinde, yapacak çok az işim vardı: sıfırlama devresi. Panoya bir düğme ekledim ve bir tarafı yüksek tutmak için 10K direnç kullandım. Diğer taraf doğrudan yere gider. Yüksek tutulan taraf, /RESET pini (CPU ve çıkış mandalı) ile her çipe giden /RESET çıkışıdır. Açılışta sıfırlamayı gerçekleştirmek için /RESET çıkışına bir kapasitör ekledim. Buradaki fikir, büyük değerli direncin, nispeten büyük kapasitörün yavaş şarj olmasına ve /RESET pinlerini bir miktar saat döngüsü için düşük tutmasına neden olacağıdır (CPU'nun dört saat döngüsüne ihtiyacı vardır). Muhtemelen bu devrenin olumsuz tarafının ne olduğunu tahmin edebilirsiniz. Aynı devre olduğu için önceki versiyonla aynı negatif. Düğmeye basıldığında, kapasitör esasen düğme aracılığıyla kısa devre yapar. Bu hem kapak hem de düğme için kötüdür, bu nedenle yapınızı biraz daha kalıcı hale getirmek istiyorsanız yeniden tasarlamak isteyebilirsiniz. Monostable modda ayarlanmış başka bir 555 zamanlayıcı düşünüyordum. Ama bununla, bilgisayar devresi artık bitti. Yay. Şimdi programlanması gerekiyor.

Adım 6: Programlama

Bu şeyi programlamak bir kabustu. Bir Arduino EEPROM programcısı yaptım. Çalışmadı. Başka birinin tasarımına ve kodlamasına dayanarak bir tane daha yaptım. Yine de çalışmadı. Adresleri ve veri baytlarını elle ayarlamanın denenmiş ve gerçek yöntemine geri döndüm. Her nasılsa, bunu mahvettim. Tekrar denedim yine hata verdi. Yine geri döndüm ve tek bir baytlık olduğunu keşfettim, bu yüzden düzelttim ve sonunda işe yaradı, şükürler olsun.

n

Asıl programa gelince, süper karmaşık ve takip etmesi zor görünüyor, ama değil. Aslında oldukça basit. Bunun yarısı etrafındaki sayıları kopyalıyor. Diğer yarısı 16-bit matematik, koşullu atlamalar ve daha da fazla kopyalanan sayı arasında paylaşılır. Bu yüzden üzerinden geçeyim ve size nasıl çalıştığını anlatayım.

n

Başlatma, program tarafından kullanılmak üzere yalnızca bazı kayıt değerlerini ayarlar. Program döngüsü biraz daha karmaşıktır, ancak çok fazla değil. İlk olarak, 00 portundaki A kaydına girişi kabul eder. Daha sonra E kaydı belleğe yazılır. İlk iki döngüde, E kaydı önemsiz veriler içerir, bu nedenle aslında yazılmayacağı için onu ROM alanının son iki baytına yazmaya çalışırız; adres işaretçisi (IY) daha sonra artırılır. D'de saklanan değer daha sonra yazılmak üzere E'ye taşınır. A daha sonra D'ye yüklenir ve L ve E, H'ye kopyalanır. HL, değer karşılaştırmasının çıkarma ve ZF (sıfır bayrağı) kontrolü yoluyla gerçekleştiği yerdir. Karşılaştırılan ilk değer, B ve C kayıtlarında saklanır. B ve C, tek bir 16 bitlik kayıt, BC olarak değerlendirilir. Değerler aynıysa, program doğrudan kullanıcı kodunun bulunduğu varsayılan RAM alanına atlar. BC'deki kod bir eşleşme değilse, HL, D ve E'den gelen başlangıç değerleriyle yeniden yüklenir ve BC ile karşılaştırıldığında aynı şekilde SP'deki değerle tekrar karşılaştırılır. Bir eşleşme ise, aynı sonuca sahiptir, ancak belleğe fazladan üç bayt yazılır. Baytlar, CPU'nun programının en başına (bir yazılım sıfırlaması) geri dönmesine neden olan bir koddur. Ancak ikinci karşılaştırma bir eşleşme değilse, program kullanıcıdan bir değer aldığı yere döner.

n

LD SP, EDBFH; exe kodu (atlama ekler)

n

LD IY, FFEH; kod depolama için ilk bellek işaretçisi

n

LDBC, EDC3H; exe kodu (döngü yok)

n

döngü; assembler yönergesi sayesinde bu bölümün bellekte nerede olduğunu bilmemize gerek kalmaz

n

İN A, (00H); program verilerini al

n

LD (IY+00H), E; E saklanacak kodu içerir

n

INC IY; sonraki hafıza konumuna git

n

LDE, D; ld D'den E'ye

n

LDD, A; ld A'dan D'ye

n

LDH,E; ld E'den H'ye

n

LDL,D; ld D'den L'ye

n

VEYA A; taşıma bayrağını sıfırla

n

SBC HL, BC; exe kodu 2 girildiyse 0 döndürür

n

JPZ, 1000H; öyleyse, programa atlayın ve çalıştırın

n

LDH,E; aksi takdirde, bunları uygun değerlere yenileyin

n

LD L, D

n

VEYA A; ilk çıkarma, taşıma bayrağını ayarlamış olabilir. Temizle

n

SBC HL, SP; exe kodu 1 girildiyse 0 döndürür

n

JP NZ, döngü; değilse, işlemi tekrarlayın (bir değer alarak başlayarak)

n

LD (IY+00H), C3H; aksi takdirde, kullanıcı programının sonuna bir atlama kodu enjekte edin

n

LD (IY+01H), 00H; atlama temelde bir yazılım sıfırlama işlevi görür

n

LD (IY+02H), 00H; kayıtların değiştirilmesi durumunda tam bir sıfırlama

n

JP 1000H; kullanıcı programına atla ve çalıştır

Önerilen:

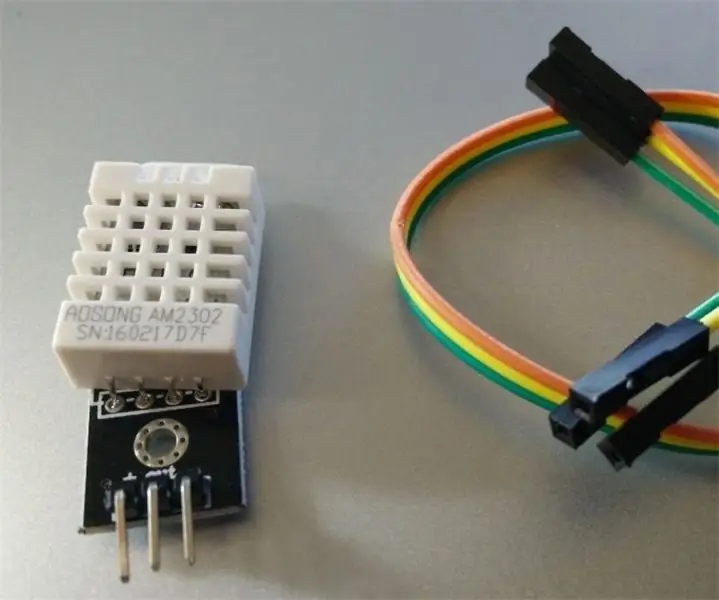

StandardFirmata'nın Ötesine Geçmek - Tekrar Ziyaret: 5 Adım

StandardFirmata'nın Ötesine Geçmek - Tekrar Ziyaret Edildi: Kısa bir süre önce, bir pymata4 kullanıcısı olan Dr. Martyn Wheeler, pymata4 kitaplığına DHT22 Nem/Sıcaklık sensörü desteği ekleme konusunda rehberlik için benimle iletişime geçti. Pymata4 kütüphanesi, Arduino muadili FirmataExpre ile birlikte

Eski Telefonu Tekrar Çaldırmak: 4 Adım

Eski Telefonu Tekrar Çaldırmak: Merhaba, benim adım Lazar ve bu benim ilk Eğitilebilir Dersim. Burada eski telefonu, içinden çıkan ağaç telleri ile yeni bir sisteme sadece iki tel ile nasıl bağladığımı göstereceğim ve açıklayacağım. Bunu düzeltmek oldukça kolaydı ve kısa ve net olacak

Eski Bir Motorola Dizüstü Bilgisayarını Kaydetme: 9 Adım

Eski Bir Motorola Dizüstü Bilgisayarını Kurtarmak: Geçenlerde, 10€'ya satılan, çok az kullanılmış bir Motorola Dizüstü Bilgisayarına rastladım. Dizüstü bilgisayarın ne olduğu hakkında hiçbir fikrim olmadan, biraz araştırdım ve harici bir monitör, klavye, pil dokunmatik yüzey, hoparlörler ve bir USB hub olarak tasarlandığını öğrendim

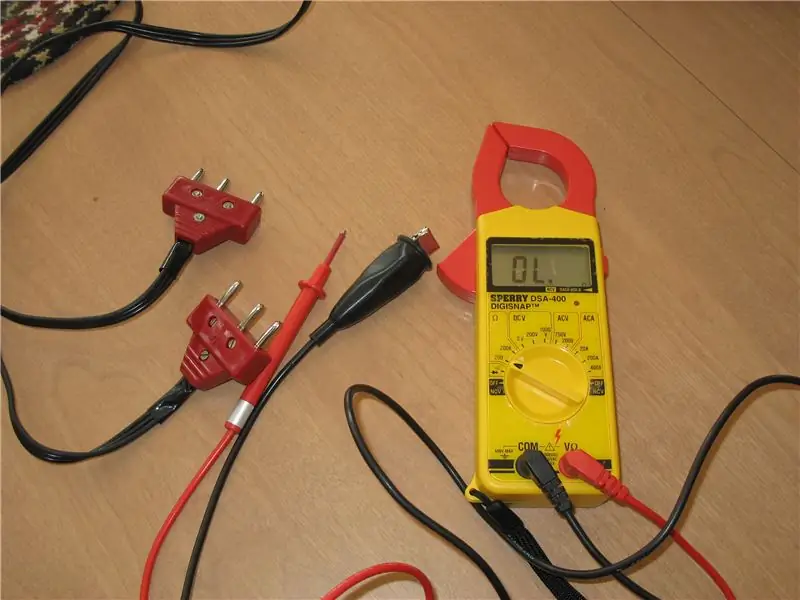

Epe Kordonunu Test Etme ve Tamir Etme: 9 Adım (Resimlerle)

Bir Epe Bodycord'un Test Edilmesi ve Onarılması: Modern, Olimpik tarzdaki eskrim sporunda, puanlama elektrikle yapılır. Elektrik sinyalinin silahınızdan puanlama makinesine gitmesi için, sinyalin silahınızdaki bir tel aracılığıyla (kılıç hariç) kolunuzdan yukarı ve aşağı hareket etmesi gerekir

Tek Yönlü WIFI Menzil Genişletici - Tekrar Ziyaret Edildi: 3 Adım

Tek Yönlü WIFI Menzil Genişletici - Tekrar Ziyaret Edildi: 1. Adım - bu bağlantıya gidin: (Sonra buraya geri gelin)https://www.instructables.com/id/Uni-Directional-WIFI-Range-Extender/?ALLSTEPS"tm36usa" Bunu Temmuz 2006'da yayınladım. Sonunda Nisan 2009'da bir tane yapmaya başladım çünkü çok seyahat ediyorum