İçindekiler:

- Adım 1: Yeniden Önyargı Aşaması

- Adım 2: Akım Algılama Direnci

- Adım 3: İletkenlik Amplifikatörü

- Adım 4: Enstrümantasyon Amplifikatörü

- Adım 5: Giriş Aşaması ve Kalibrasyon

- Adım 6: Gelişmiş Öğeler: Spektral Sızıntı (DC)

- 7. Adım: Gelişmiş Öğeler: Spektral Sızıntı (AC)

- Adım 8: Gelişmiş Öğeler: Teorik Kazanç faktörü

- 9. Adım: Gelişmiş Öğeler: PA Kayması

- Yazar John Day day@howwhatproduce.com.

- Public 2024-01-30 13:19.

- Son düzenleme 2025-06-01 06:10.

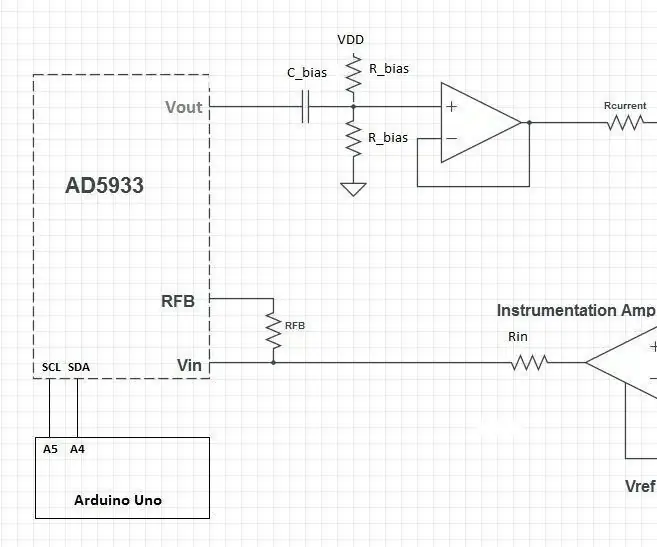

Vücut kompozisyonu ölçümleri için bir Biyo Empedans Analizörü yapmakla ilgileniyordum ve rastgele aramalarım Vanderbilt Üniversitesi'ndeki 2015 Biyomedikal Enstrümantasyon sınıfından bir tasarım bulmaya devam etti. Tasarım üzerinde çalıştım ve biraz geliştirdim. Bulgularımı sizinle paylaşmak istiyorum. Bir şey net değilse, bu "geçişten" yararlanabileceğinizi alın, lütfen iyileştirmeler önerin. Bir gün düşüncelerimi daha uyumlu bir biçimde yazabilirim, ama şimdilik burada ne görüyorsanız onu kullanabileceğinizi umuyorum. (Bunu yazıp geliştirebileceğinizi düşünüyorsanız, bekliyoruz)

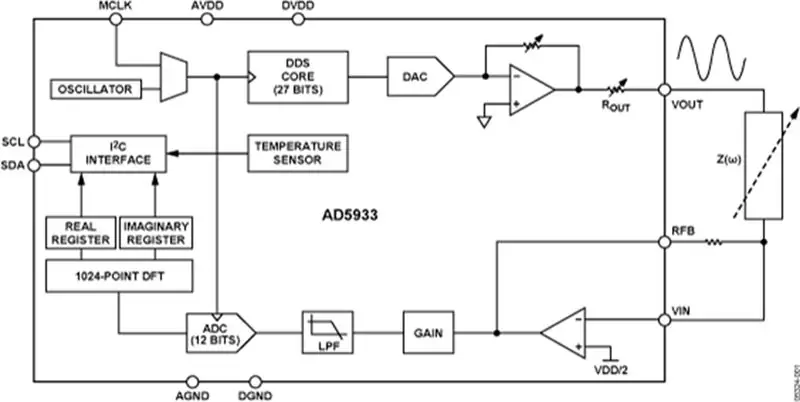

oyuncak

Bu tasarım, AD5933 çipinden ve AD5933'ü gövdeyle arayüzlemek için özel bir analog ön uçtan (AFE) oluşur. AD5933 daha sonra ölçümü yapar ve sonuçlar daha sonra bir mikro denetleyici (örneğin bir Arduino) tarafından işlenebilir.

Arduino'yu bir güç kaynağı olarak kullanmayı planlıyorsanız, operasyonel ve enstrümantasyon amplifikatörlerinin (op-amp'ler ve in-amp'ler) "tek besleme" voltajlarını desteklediğinden ve raydan raya teknik özelliklere sahip olduğundan emin olun.

(Aşağıda 5V'luk bir güç kaynağı (Arduino'dan) ve AD5933'teki Aralık 1 ayarını kullanacağım.)

Adım 1: Yeniden Önyargı Aşaması

AFE'nin ilk kısmı bir yeniden önyargı aşamasıdır. Çıkış voltajı sinyali, besleme voltajı aralığının (VDD/2) ortasında ortalanmamıştır. Bu, sinyalin DC kısmını bloke etmek için bir kapasitör kullanılarak ve sinyale bir DC ofseti eklemek için bir voltaj ayırıcıdan gönderilerek düzeltilir.

İki yeniden önyargı direnci, aynı oldukları sürece herhangi bir değer olabilir. Başlığın özel değeri de önemli değildir.

Yeniden önyargı aşaması, yüksek geçiş filtresi gibi çalışır ve bu nedenle bir kesme frekansına sahiptir:

f_c = 1 / (2*pi * (0,5*R) * C)

Kesme frekansının kullanmayı planladığınız minimum frekansın birkaç on yıl altında olduğundan emin olun. Uygulamanızda 1kHz kullanmayı planlıyorsanız, size 1-10 Hz mertebesinde bir kesme frekansı verecek olan kapaklar ve direnç değerlerine gitmelisiniz.

Bu aşamanın son kısmı, voltaj takipçisi olacak şekilde ayarlanmış bir op-amp'dir. Bu, direnç değerlerinin bir sonraki aşamaya müdahale etmemesini sağlamak içindir.

Adım 2: Akım Algılama Direnci

Bir sonraki aşamanın ilk kısmı, mevcut algılama direncidir. Bu dirençten geçen akım, amplifikatörün gövde boyunca sürdürmeye çalışacağı akımla aynı olacaktır. Akımın IEC6060-1 güvenlik standartlarına* uygun olduğundan emin olun:

1 kHz'lik frekansların altında, vücuttan maksimum 10 mikroAmp(RMS) izin verilir. 1kHz'in üzerindeki frekanslarda, aşağıdaki denklem izin verilen maksimum akımı verir:

Maks AC akımı < (kHz cinsinden minimum frekans) * 10 mikroAmp(RMS)

Bir AC sinyalinin tepe genliği ile RMS değeri arasındaki ilişki şöyledir: Tepe = sqrt(2) * RMS. (10 mikroAmp RMS, 14 mikroAmp tepe genliğine karşılık gelir)

Direnç üzerindeki Ohm Yasasını kullanarak güvenlik standardına uygun olacak direnç değerini hesaplayabiliriz. AD5933'ten gelen uyarma voltajını ve maksimum akım değerini kullanıyoruz:

U = R * I => R = U / I

Örneğin. Aralık 1 ayarını kullanarak Yukarı = 3V / 2 = 1.5V (veya 1V @3.3V)

Yukarıdan 14 microAmp tepe değerini kullanarak en az 107kOhms'luk bir direnç değeri alıyorum

Referanslar:

* Analog Cihazlar: "Vücut Aşınmış Sistemler için Biyo-Empedans Devre Tasarımı"

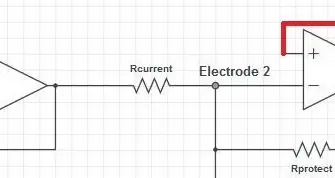

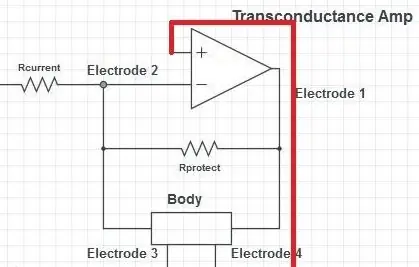

Adım 3: İletkenlik Amplifikatörü

Mevcut algılama direncinden sonra, negatif geri besleme konfigürasyonunda bir op-amp vardır. Bu, Loop'ta Yükleme kurulumu olarak adlandırılan bir kurulumdur. Op-amp'nin pozitif giriş terminali bir VDD/2 voltajına bağlanır. Op-amp şimdi çıkışını uyarma sinyaline ters yönde, negatif terminaldeki voltajın VDD/2'ye eşit olacağı şekilde ayarlamaya çalışacaktır. Bu, akımı vücuttan iten ve çeken bir tahterevalli potansiyeli üretecektir.

Op-amp'in negatif terminalinden çekilen akım neredeyse sıfırdır. Akım algılama direncinden geçen tüm akım bu nedenle gövdeden akmak zorundadır. Bu kurulumu bir trans-iletkenlik yükselticisi yapan mekanizma budur (voltaj kontrollü akım kaynağı, VCCS olarak da adlandırılır).

Op-amp yalnızca gövdenin empedansı çok yüksek değilse akımı koruyabilir. Aksi takdirde, op-amp çıkışı, besleme geriliminde (0 veya 5 V) maksimuma çıkar. Korunabilecek maksimum voltaj aralığı VDD/2 + Upeak'tir (2.5+1.5V = 4V @ 5V besleme). Op-amp'nin voltaj marjları bu değerden çıkarılmalıdır, ancak op-amp'in raydan raya özellikleri varsa, bu sadece küçük bir miktar olacaktır. Op-amp'in sürebileceği maksimum empedans bu nedenle:

Z < (VDD/2 + Yukarı) / Imaks

(Benim kurulumumda Z < 4V / 14 microAmps = 285 kOhm, gövdenin empedans aralığını kapsamak için dilek bol)

Koruyucu direnç, gövdeye (yaklaşık 100kOhms) kıyasla çok büyük bir değere (1-1,5 MOhms) sahiptir ve tüm normal işlemler için bu, fark edilir bir akım çekmez ve paralel bağlantının empedansına gövdenin empedansı hakimdir. Gövdenin empedansı yükselirse (örneğin pedler gevşerse), akım dirençten geçebilir ve op-amp'in maksimuma çıkarılması pedlerde istenmeyen voltajlar yaratmaz.

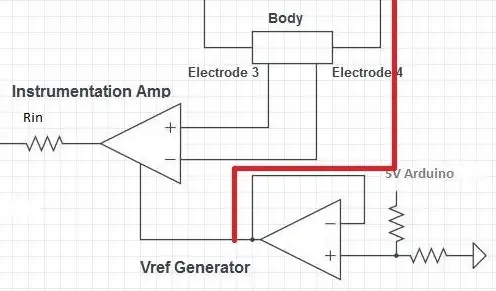

Adım 4: Enstrümantasyon Amplifikatörü

Bir sonraki aşama, vücuttaki voltajı ölçen enstrümantasyon amplifikatörüdür (amper içi). Gövde üzerindeki voltaj 0V civarında salınım yapıyor, ancak AD5933'ün giriş voltajının pozitif bir aralıkta olması gerekiyor. Bu nedenle in-amp, ölçülen voltaj sinyaline VDD/2'lik bir DC ofseti ekler.

VDD/2 referansı, bir voltaj bölücü tarafından üretilir. Herhangi bir değer direnci, aynı oldukları sürece kullanılabilir. Gerilim bölücü, bir gerilim takipçisi ile devrenin geri kalanının empedansından ayrılır. Voltaj izleyicinin çıkışı daha sonra hem ampliye hem de trans-iletkenlik yükselticisine iletilebilir.

Adım 5: Giriş Aşaması ve Kalibrasyon

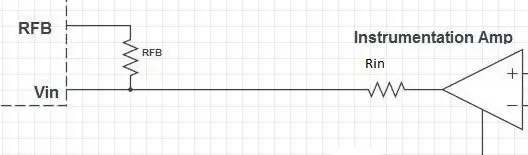

AD5933'ün giriş aşaması, negatif geri besleme konfigürasyonunda bir op-amp içerir. İki direnç vardır: biri seri (Rin) ve diğeri paralel (RFB). Op-amp'in kazancı şu şekilde verilir:

A = - RFB / Durulama

Giriş op-amp'inin ve amfinin (ve PGA'nın) kazanımları, AD5933'ün ADC'sine giden sinyalin her zaman 0V ve VDD içinde olduğundan emin olmalıdır.

(Yaklaşık A = 0,5 verecek bir birlik kazancı amper ve direnç değerleri kullanıyorum)

AD5933'ün içinde ADC, voltaj sinyalini dijital bir sinyale dönüştürecektir. 0V ile VDD arasındaki voltaj aralığı 0-128 (2^7) dijital aralığına dönüştürülür. (Bununla ilgili belgeler net değil, ancak [1]'deki parsellerin yakından incelenmesi ve benim tarafımdan yapılan bazı deneyler bunu doğruluyor.)

Sonuç gerçek ve sanal kayıtta kaydedilmeden önce DFT modülünün içinde başka bir 256 (1024/4, [1]'e bakınız) ölçekleme vardır.

AFE'den gelen voltaj sinyalini ADC'ye takip ederek ve daha önce bahsedilen ölçek faktörlerini kullanarak kazanç faktörünü şu şekilde tahmin etmek mümkündür:

g = (VDD * Rcurrent * Rin) / (256 * PGA * Upeak * RFB * 2^7)

Bazı kalibrasyonlar hala gerekli olabilir, bu nedenle bu matematiksel modelin parçası olmayan bazı etkileri hesaba katın, bu nedenle lütfen dirençler gibi bilinen empedansın bileşenlerini ölçerek gerçek kazanç değerini ölçün. (g = Z / mag, aşağıya bakın)

Empedans şimdi şu şekilde hesaplanabilir:

Z = g * mag

mag = kare(gerçek^2 + hayali^2)

PA = arctan2(gerçek, hayali) - deltaPA

AD5933'te frekansın bir fonksiyonu olarak sistematik bir faz kayması olduğu gibi PA'nın muhtemelen kalibre edilmesi gerekir. deltaPA muhtemelen frekansın bir doğrusal fonksiyonu olacaktır.

Direnç ve reaktans şimdi şu şekilde hesaplanabilir:

R = Z * cos(PA)

X = Z * günah(PA)

Referanslar:[1] Leonid Matsiev, "AD5933 gibi Tek Frekanslı DFT Dedektörlerine Dayalı Sistemlerin Performansını ve Çok Yönlülüğünü Geliştirme", Electronics 2015, 4, 1-34; doi:10.3390/elektronik4010001

Adım 6: Gelişmiş Öğeler: Spektral Sızıntı (DC)

AD5933'e koyduğumuz sinyal, zamanın bir işlevi olarak bir voltaj/akımdır, ancak asıl ilgi alanımız, frekansın bir işlevi olarak empedanstır. Zaman alanı ve frekans alanı arasında dönüşüm yapmak için zaman alanı sinyalinin Fourier dönüşümünü almamız gerekir. AD5933, yerleşik bir ayrık Fourier dönüşümü (DFT) modülüne sahiptir. Düşük frekanslarda (yaklaşık 10 kHz'in altında), DFT'deki yapı, örtüşme ve spektral sızıntılardan etkilenir. [1]'de spektral sızıntının nasıl düzeltileceğinin matematiğini inceliyor. Bunun özü, taramadaki her frekans adımı için beş (artı iki) sabit hesaplamaktır. Bu kolayca yapılabilir; Arduino tarafından yazılımda.

Kaçak iki şekilde gelir: doğası gereği katkı olan bir DC kaçağı ve doğada çoğaltıcı olan bir AC kaçağı.

DC sızıntısı, ADC'deki voltaj sinyalinin 0V civarında değil, VDD/2 civarında salınmasından kaynaklanmaktadır. Bir DC VDD/2 seviyesi, yaklaşık 64'lük bir dijital DC okumasına karşılık gelmelidir ([1'de belirtilen delta).

DC spektral sızıntıyı düzeltme adımları:

1) Mevcut frekans için Zarf faktörü E'yi hesaplayın.

2) GI (gerçek) ve GQ (hayali) olmak üzere iki kazanç faktörünü hesaplayın

3) Gerçek kaydın değerinden delta * GI'yi ve sanal kaydın değerinden delta * GQ'yu çıkarın

Referanslar:

[1] Leonid Matsiev, "Sistemlerin Performansını ve Çok Yönlülüğünü Geliştirmek

AD5933 gibi Tek Frekanslı DFT Detektörleri, Electronics 2015, 4, 1-34; doi:10.3390/electronics4010001

[2] Konrad Chabowski, Tomasz Piasecki, Andrzej Dzierka, Karol Nitsch, "AD5933 Entegre Devresine Dayalı Basit Geniş Frekans Aralığı Empedans Ölçer", Metrol. Ölçü. Syst., Cilt. XXII (2015), No. 1, s. 13-24.

7. Adım: Gelişmiş Öğeler: Spektral Sızıntı (AC)

DC kaçağı gibi, AC kaçağı da matematiksel olarak düzeltilebilir. [1]'de direnç ve reaktans sırasıyla A*cos(phi) ve A*sin(phi) olarak adlandırılır, burada A empedansın büyüklüğüne karşılık gelir ve phi faz açısına (PA) karşılık gelir.

AC spektral sızıntıyı düzeltme adımları:

1) Mevcut frekans için Zarf faktörü E'yi (DC ile aynı değil) hesaplayın.

2) a, b ve d faktörlerini hesaplayın. (daha yüksek frekanslarda yaklaşık değerler: a = d = 256 ve b = 0)

3) Direnç (Acos(phi)) ve reaktans (Asin(phi)) artık dijital birimlerde hesaplanabilir

Referanslar:[1] Leonid Matsiev, "AD5933 gibi Tek Frekanslı DFT Dedektörlerine Dayalı Sistemlerin Performansını ve Çok Yönlülüğünü Geliştirme", Electronics 2015, 4, 1-34; doi:10.3390/elektronik4010001

[2] Konrad Chabowski, Tomasz Piasecki, Andrzej Dzierka, Karol Nitsch, "AD5933 Entegre Devresine Dayalı Basit Geniş Frekans Aralığı Empedans Ölçer", Metrol. Ölçü. Syst., Cilt. XXII (2015), No. 1, s. 13-24.

Adım 8: Gelişmiş Öğeler: Teorik Kazanç faktörü

DFT'nin matematiksel modellemesi göz önüne alındığında, AFE'nin tamamını matematiksel olarak modellemek de mümkün olmalıdır. Matematiksel olarak voltaj sinyali, belirli bir sabit frekansa, bir DC kaymasına ve bir tepe genliğine sahip bir AC salınımına sahip bir sinüs fonksiyonu ile tanımlanabilir. Frekans, bir frekans adımı sırasında değişmez. Kazanç faktörü PA'yı değil sadece empedansın büyüklüğünü değiştirdiği için burada sinyal üzerinde indüklenen herhangi bir faz kayması ile ilgilenmeyeceğiz.

AFE üzerinden yayılan voltaj sinyalinin kısa bir özeti aşağıda verilmiştir:

1) Yeniden önyargı aşamasından sonra AC genliği hala Yukarı=1.5V (1V @ VDD=3.3V) ve DC ofseti VDD/2 olarak değiştirilmiştir.

2) Akım algılama direncinde voltaj, önceki aşama ile aynıdır…

3) … ancak op-amp'in tahterevalli voltajı nedeniyle AC salınımlarının boyutu Z*Yukarıda/Rakımdır. (DC ofseti, tahterevallinin dönme noktası olan VDD/2'nin op-amp referans voltajı tarafından iptal edilir ve devrenin bu bölümünde bir erdemli toprak haline gelir)

4) Birlik in-amp, VDD/2'nin DC ofsetini geri ekler ve sinyali AD5933'ün giriş aşamasına iletir

5) Giriş aşamasındaki op-amp, A=-RFB/Rin kazancına sahiptir ve bu nedenle AC genliği (Z*Upeak/Rcurrent)*(RFB/Rin) olur.

6) ADC'den hemen önce, kazanç 1 veya 5 olan iki ayarlı programlanabilir bir kazanç yükselticisi (PGA) vardır. ADC'deki voltaj sinyali bu nedenle şöyle olur: PGA*(Z*Upeak/Rcurrent)*(RFB/Rin)

ADC, v(t) sinyalini 12 bitlik bir doğrulukla x(t) = u(t) / VDD * 2^7 dijital sinyaline dönüştürür.

A büyüklüğü, Z empedansına kazanç faktörü k ile A = k * Z olarak bağlanır ve yaklaşık olarak k = PGA * Upeak * RFB * 2^7 / (VDD * Rcurrent * Rin) değerine sahiptir.

Kazanç faktörü ile çalışmayı seviyorsanız bunun yerine g = 1 / k ve Z = g * A.

9. Adım: Gelişmiş Öğeler: PA Kayması

[2]'de, frekansın bir fonksiyonu olarak PA'da sistematik bir kayma buluyorlar. Bunun nedeni, uyarma sinyalinin üretildiği DAC ile gelen sinyalin giden sinyal ile kıvrılması gereken DFT arasındaki zaman gecikmesidir.

Kaydırma, AD5933'te dahili olarak DAC ve DFT arasındaki sinyalin gecikmesi olan saat çevrimlerinin sayısı ile karakterize edilir.

Referanslar:[1] Leonid Matsiev, "AD5933 gibi Tek Frekanslı DFT Dedektörlerine Dayalı Sistemlerin Performansını ve Çok Yönlülüğünü Geliştirme", Electronics 2015, 4, 1-34; doi:10.3390/elektronik4010001

[2] Konrad Chabowski, Tomasz Piasecki, Andrzej Dzierka, Karol Nitsch, "AD5933 Entegre Devresine Dayalı Basit Geniş Frekans Aralığı Empedans Ölçer", Metrol. Ölçü. Syst., Cilt. XXII (2015), No. 1, s. 13-24.

Önerilen:

Bölüm 1. ThinkBioT Otonom Biyo-akustik Sensör Donanım Yapısı: 13 Adım

Bölüm 1. ThinkBioT Otonom Biyo-akustik Sensör Donanım Yapısı: ThinkBioT, veri toplama, ön işleme, veri iletimi ve görselleştirme görevlerinin ayrıntılarını ele alarak, daha fazla araştırmayı desteklemek için teknolojik bir omurga olarak tasarlanmış bir yazılım ve donanım çerçevesi sağlamayı amaçlar. araştırmacı

Erişilebilirlik veya Eğlence için Biyo-Uyarlanabilir Medya Denetleyicisi: 7 Adım

Erişilebilirlik veya Eğlence için Biyo-Uyarlamalı Medya Denetleyicisi: Bu talimatta, tıpkı geliştirdiğim açık kaynaklı sistem gibi Arduino kullanarak kendi biyo-optimize edilmiş medya denetleyicinizi nasıl oluşturacağınızı öğreneceksiniz. Ek bir hızlı açıklama için bağlantılı videoyu izleyin. Bir tane oluşturur ve daha fazla test yaparsanız

Renk Sensörü ile Sipariş Defteri Analizi: 14 Adım

Renk Sensörü ile Sipariş Defteri Analizi: Kripto ticareti yaparken ekrandaki sipariş defterinden gelen ışık çıkışını analiz etmek için bir Adafruit TCS34725 kırmızı/yeşil/mavi renk sensörü kullanır. Ağırlıklı olarak "satın al" ise; Ekranda yeşil sayılarla gösterilen siparişler gelir, muhtemelen bekleyebilirsiniz

Raspberry Pi ile Twitter Duygu Analizi: 3 Adım (Resimlerle)

Raspberry Pi ile Twitter Duygu Analizi: Duygu analizi nedir ve bunu neden önemsemelisiniz? Duygu analizi, ifade edilen tutum, görüş ve duyguları anlamak için kullanılan bir dizi kelimenin arkasındaki duygusal tonu belirleme sürecidir. içinde

Biyo İzleme: 8 Adım (Resimlerle)

Bio Monitoring: Herkese merhaba,Bir öğrenci projesi kapsamında bizden tüm süreci anlatan bir makale yayınlamamız istendi.Ardından size bio izleme sistemimizin nasıl çalıştığını sunacağız.Taşınabilir bir cihaz olması amaçlanmıştır. nem,