İçindekiler:

- Yazar John Day day@howwhatproduce.com.

- Public 2024-01-30 13:19.

- Son düzenleme 2025-01-23 15:13.

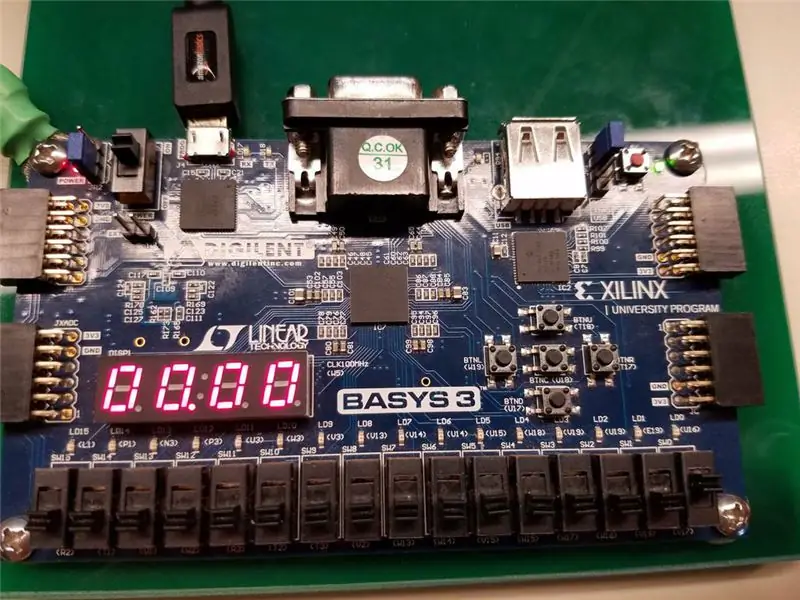

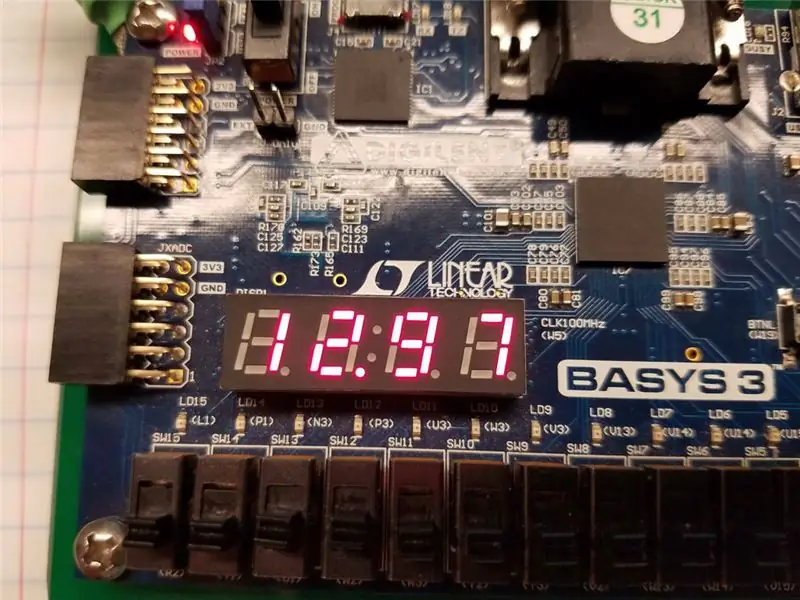

Temel VHDL ve Basys 3 kartını kullanarak bir kronometrenin nasıl oluşturulacağına ilişkin talimata hoş geldiniz. Projemizi sizinle paylaşmaktan heyecan duyuyoruz! Bu, Güz 2016'da Cal Poly, SLO'da CPE 133 (Dijital Tasarım) kursu için son bir projeydi. Oluşturduğumuz proje, zamanı başlatan, sıfırlayan ve duraklatan basit bir kronometredir. Basys3 kartında giriş olarak üç adet basma düğmesi alır ve saat, kartın dört haneli yedi segmentli ekranında görüntülenir. Geçen süre, saniye cinsinden görüntülenir: santimetre saniye biçiminde. Geçen süreyi takip etmek için giriş olarak kartın sistem saatini kullanır ve zamanı yedi bölümlü ekranın dört hanesine verir.

Adım 1: Malzemeler

Bu proje için ihtiyacınız olacak malzemeler:

- Xilinx'ten Vivado Design Suite WebPack yüklü 1 bilgisayar (2016.2 sürümünü tercih edin)

- 1 Digilent Basys3 Xilinx Artix-7 FPGA kartı

- 1 USB bağlantı noktası kablosu

Adım 2: Giriş ve Çıkışların Ayarlanması

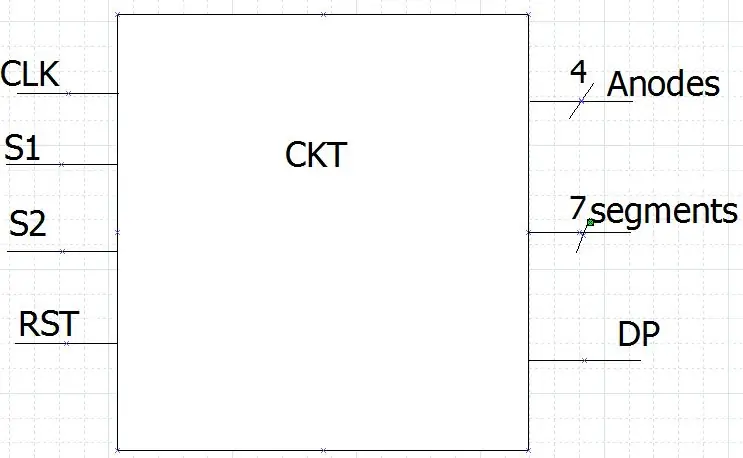

Yukarıdaki şekil, ana kronometre modülünün en üst seviye blok şemasını göstermektedir. Kronometre, "CLK" (saat), "S1" (başlat düğmesi), "S2" (duraklatma düğmesi) ve "RST" (sıfırlama) girişlerini alır ve 4 bitlik "Anotlar", 7 bitlik bir çıkışa sahiptir. çıkış "segment" ve bir tek bitlik çıkış "DP" (ondalık nokta). "S1" girişi yüksek olduğunda, kronometre zamanı saymaya başlar. "S2" düşük olduğunda, kronometre zamanı duraklatır. "RST" yüksek olduğunda, kronometre durur ve zamanı sıfırlar. Devrede dört alt modül vardır: saat bölücü, sayı sayacı, yedi segmentli ekran sürücüsü ve yedi segmentli ekran kodlayıcı. Kronometre ana modülü, tüm alt modülleri birbirine ve giriş ve çıkışlara bağlar.

3. Adım: Saat Yapmak

Saat bölücü modülü bir sistem saatini alır ve sistem saatinden daha büyük olmayan herhangi bir hızda bir saat oluşturmak için bir bölen girdi kullanır. Kronometre, biri 500 Hz saat oluşturan ve diğeri 100 Hz saat oluşturan iki farklı saat modülü kullanır. Saat bölücünün şeması yukarıdaki şekilde gösterilmiştir. Saat bölücü, tek bitlik bir giriş "CLK" ve 32 bitlik bir giriş "Bölücü" ve tek bitlik bir çıkış "CLKOUT" alır. "CLK" sistem saatidir ve "CLKOUT" sonuç saatidir. Modül ayrıca, sayı bölen değerine ulaştığında "CLKTOG" sinyalini değiştiren bir DEĞİL kapısı içerir.

Adım 4: Ona Kadar Sayma

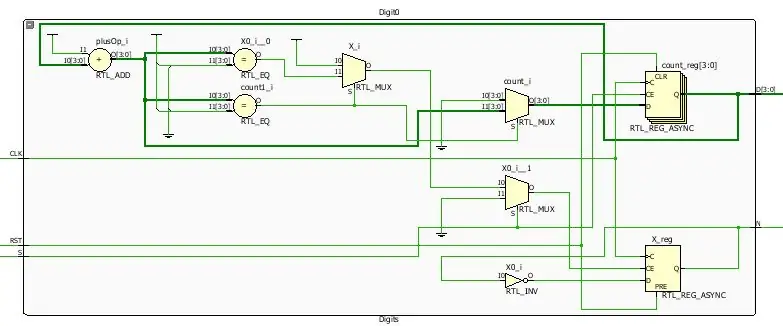

Rakam sayacı, 0'dan 10'a kadar olan her basamağı sayar ve sayım 10'a ulaştığında salınan bir sonraki basamağın çalışması için başka bir saat oluşturur. Modül, "S", "RST" ve "CLK" olmak üzere 3 adet tek bitlik giriş alır. " ve tek bit çıkış "N" ve 4 bit çıkış "D" ile sonuçlanır. "S" girişi, girişteki etkinleştirmedir. "S" yüksek olduğunda saat açılır ve "S" düşük olduğunda kapanır. "RST", sıfırlama girişidir, bu nedenle "RST" yüksek olduğunda saat sıfırlanır. "CLK", rakam sayacı için saat girişidir. "N", bir sonraki basamak için giriş saati haline gelen saat çıkışıdır. "D" çıkışı, sayacın bulunduğu basamağın ikili değerini sunar.

Adım 5: Sayıları Görüntüleme

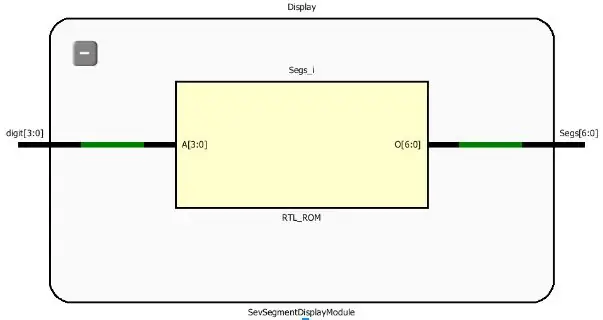

Yedi bölümlü görüntü kodlayıcı, yedi bölümlü görüntü sürücü modülünden alınan ikili sayıyı kodlayacak ve onu ekranın her bölümü için '1' veya '0' değerleri olarak yorumlanacak bir bit akışına dönüştürecektir. İkili sayı, modül tarafından 4 bitlik giriş "rakam" olarak alınır ve 7 bitlik çıkış "segmentleri" ile sonuçlanır. Modül, 0 ila 9 arasındaki her olası giriş değeri için belirli bir 7 bitlik akış atayan tek bir durum işlem bloğundan oluşur. Yedi bitlik akışlardaki her bit, ekrandaki rakamların yedi bölümünden birini temsil eder. Akıştaki bölümlerin sırası "abcdefg" şeklindedir ve '0'lar verilen sayı için yanan bölümleri temsil eder.

Adım 6: Kronometre Nasıl Görüntülenir

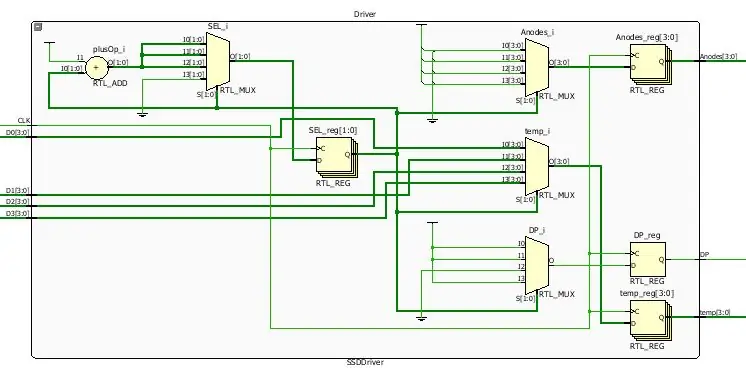

Yedi bölümlü ekran sürücüsü modülünde, her biri görüntülenecek dört basamağı temsil eden "D0", "D1", "D2" ve "D3" olmak üzere dört adet 4 bitlik giriş vardır. "CLK" girişi, sistemin saat girişidir. Tek bitlik çıkış "DP", yedi bölümlü ekrandaki ondalık noktayı temsil eder. 4 bitlik çıkış "Anotlar", yedi segmentli ekranda hangi rakamın gösterileceğini belirler ve 4 bitlik çıkış "temp", 2 bitlik kontrol girişi "SEL"in durumuna bağlıdır. Modül, "SEL" kontrol girişi ve üç çıkış için 4 çoklayıcı kullanır; "Anotlar", "temp" ve "DP".

7. Adım: Hepsini Bir Araya Getirmek

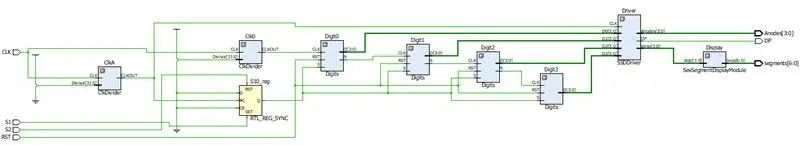

Başlatma ve duraklatma düğmelerini oluşturmak için 500 Hz'lik saatten çalışan bir 'if' işlem bloğu kullanılır. Ardından, her bir alt modülün bileşenlerini bildirerek ve çeşitli sinyaller kullanarak tüm alt modülleri kronometre ana modülünde birbirine bağlayın. Rakam alt modülleri, ilki 100Hz saati alarak önceki rakam alt modülünün saat çıkışını alır. Rakam alt modüllerinin "D" çıkışları daha sonra yedi segmentli ekran sürücü modülünün "D" girişleri olur. Ve son olarak, yedi segmentli ekran sürücü modülünün "temp" çıkışı, yedi segmentli enkoder modülünün "temp" girişi olur.

8. Adım: Kısıtlamalar

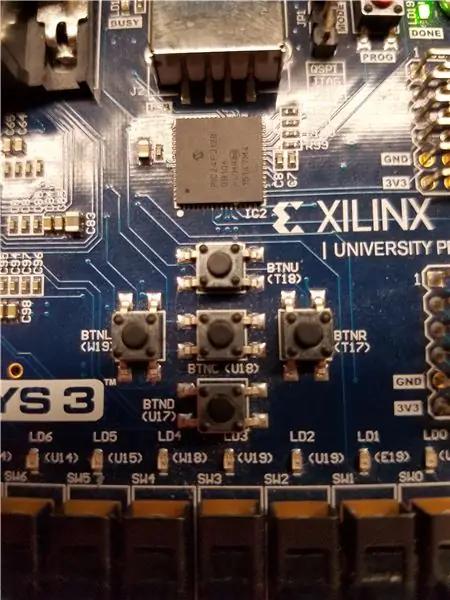

"RST", "S1" ve "S2" girişleri için 3 basmalı düğmeyi (W19, T17 ve U18) kullanın. W19 sıfırlama düğmesi, T17 başlatma düğmesi (S1) ve U18 duraklatma düğmesidir (S2). W5 bağlantı noktası kullanılarak saat girişi girişi için bir kısıtlama da gereklidir. Ayrıca, bu satırı saat kısıtlamasına eklemeyi unutmayın:

create_clock -add -name sys_clk_pin -period 10.00 -waveform {0 5} [get_ports {CLK}]

Kronometrenin kısıtlamalar dosyasında görüldüğü gibi yedi segmentli ekranda görüntülenmesi için ayrıca Anotları ve segmentleri panoya bağlayın.

9. Adım: Test Etme

Üç düğmeyle oynayarak cihazınızın çalıştığından emin olun: kodunuzla ilgili olası sorunları bulmak için bunları mümkün olan her sırada basılı tutun.

Önerilen:

NAIN 1.0 - Arduino Kullanan Temel İnsansı Robot: 6 Adım

NAIN 1.0 - Arduino Kullanan Temel İnsansı Robot: Nain 1.0, temelde 5 ayrılabilir modüle sahip olacaktır- 1) Arm - servolar ile kontrol edilebilir. 2) Tekerlekler - dc motorlarla kontrol edilebilir. 3) Bacak - Nain, hareket için tekerlekler veya bacaklar arasında geçiş yapabilecektir. 4) Baş ve

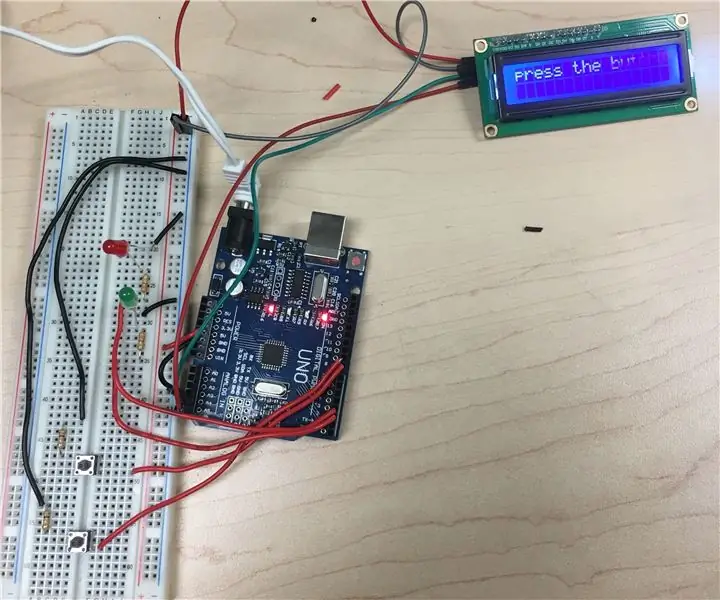

I2C LCD Kullanan Arduino Kronometre: 5 Adım

I2C LCD Kullanan Arduino Kronometre: Bu projede size interaktif kronometre olarak bir LCD ekran ve bir Arduino kullanmayı öğreteceğim. Verilen kod ile projeniz bittiğinde yukarıdaki fotoğraftaki gibi görünmelidir. Nereden başlayacağınızı öğrenmek için sonraki adıma geçin

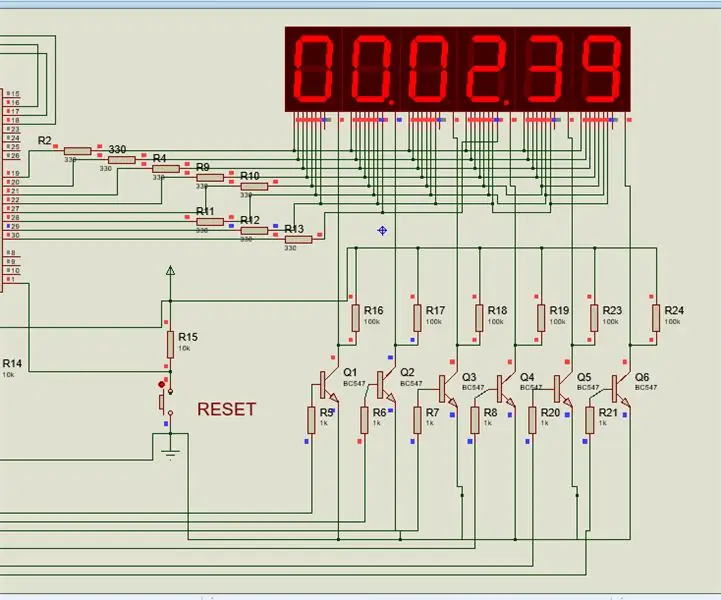

Proteus'ta Pic18f4520 Kullanan Kronometre 7 Segmentli: 6 Adım

Proteus'ta Pic18f4520 Kullanımı 7 Segmentli Kronometre: Pic controller ile çalışmaya yeni başladım, bir arkadaşım ondan bir kronometre yapmamı istedi. Yani paylaşacak donanım imajım yok, Proteus yazılımında kod yazıp simüle ettim.Burada aynı şemayı paylaştım.t

VHDL Bir Dakika Kronometre: 5 Adım

VHDL Bir Dakikalık Kronometre: Bu, VHDL ve bir Basys 3 kartı kullanarak bir dakikalık kronometrenin nasıl oluşturulacağına dair bir eğitimdir. Böyle bir cihaz, her oyuncunun hamlesini yapmak için en fazla bir dakikası olduğu oyunlar için idealdir. Kronometre, saniyeleri ve milisaniyeleri doğru bir şekilde gösterir

VHDL Kronometre: 8 Adım (Resimlerle)

VHDL Kronometre: Bu, VHDL ve Basys3 Atrix-7 Board gibi bir FPGA devre kartı kullanarak nasıl kronometre yapılacağına dair bir eğitimdir. Kronometre 00.00 saniyeden 99,99 saniyeye kadar sayabilir. Biri başlat/durdur düğmesi için diğeri de bu düğme için olmak üzere iki düğme kullanır