İçindekiler:

- Yazar John Day day@howwhatproduce.com.

- Public 2024-01-30 13:21.

- Son düzenleme 2025-01-23 15:14.

Bu, VHDL ve bir Basys 3 kartı kullanarak bir dakikalık kronometrenin nasıl oluşturulacağına dair bir eğitimdir. Böyle bir cihaz, her oyuncunun hamlesini yapmak için en fazla bir dakikası olduğu oyunlar için idealdir. Kronometre, 0 saniye ve 0 milisaniyeden başlayarak 60 saniyeye ve 0 milisaniyeye kadar yedi segmentli ekranda saniyeleri ve milisaniyeleri doğru bir şekilde görüntüler. İki düğme de kullanılır: zamanlayıcıyı başlatmak, durdurmak ve devam ettirmek için kullanılan merkezi düğme ve zamanlayıcıyı yeniden başlatmak için kullanılan sağ düğme. Cihaz, bir akıllı telefonun dahili kronometresi ile yan yana kıyaslandığında saatin doğruluğu dikkat çekiyor.

Adım 1: Donanım/Yazılım Edinme

1. Digilent'ten Basys 3 Artix-7 FPGA Trainer Board with Micro-USB - USB Kablosu

2. Xilinx'ten Vivado 2016.2 Tasarım Paketi

Adım 2: Blok Şeması

Bu devre davranışsal olarak oluşturulmuştur ve yerleşik Xilinx bileşenlerini kullanır, ancak yukarıdaki genel yapısal diyagramda gösterildiği gibi yapısal olarak da tanımlanabilir. Şemadan, devrenin iki frekans bölücü tarafından sürüldüğü görülebilir. Frekans bölücülerden biri 1 santimetrede çalışır ve yedi segmentli ekranda görüntülenen sayılar olarak kullanılan katot sayacını çalıştırır. İkinci frekans bölücü 240 Hz'de çalışır ve anotlar arasında dönen anot sayacını sürmek için kullanılır, böylece tüm sayılar yedi segmentli ekranda doğru şekilde görüntülenir. Kodlayıcı, katot sayacından katot mantığını ve anot sayacından anot mantığını alır ve bunu çıkışın yedi segmentli ekranı çalıştıran katodu ve anoda kodlar. Bu kodlayıcının işlevi, anot çıkışı her değiştiğinde katot çıkışının değişmesi içindir. Anotların 4 ayrı basamak boyunca dönmesi gerektiğinden katot çıkışı sayaçtan bağımsız olarak çalıştırılamaz.

Adım 3: Proje Modülü

İlk olarak, CEN için bir işlem bloğu yapılır, böylece bir Düğmeye Basma algılandığında, ETKİNLEŞTİR geçiş yapar. Bu, katot sayacının durdurma/başlatma işlevi görür.

Sonraki işlem bloğunda, santisaniye ve 240Hz saat sinyalleri, dahili 100 mHz saat yükselen kenara her ulaştığında ilgili sayaçları 1 artacak şekilde ayarlanır. Santisaniye sayacı 500000'e ulaştığında, 0'a sıfırlanır. Bu arada 240Hz sayaç, sayım 41667'ye ulaştığında sıfırlanır.

Kodun katot bölümü için, ETKİNLEŞTİR '0' ise, katot sayımı duraklayacaktır. Bu süre içerisinde reset butonuna basılırsa tüm sayımlar "0000" olarak sıfırlanır. Bu arada, ETKİNLEŞTİR '1' ise, katot sayımı, durma sinyalinin '1' olmasını tetiklediği 60.00'a ulaşana kadar katot sayımı devam edecektir. Durdurma sinyali, CEN işlem bloğuna geri döner ve durdurma sinyali '1' iken ETKİNLEŞTİR'in '0' olmasına neden olur ve sıfırlama düğmesine basılana kadar değişmeyecektir.

Son olarak, yedi segmentli ekran, 4 anotun 8 katodunun her birine doğru şekilde bağlanmasıyla, 0-9 arasındaki ilgili rakamları aynı anda görüntülemek için kurulur.

4. Adım: Kısıtlamalar

Bu kısıtlama dosyası, VHDL'den belirtilen giriş ve çıkışları Basys kartının gerekli fiziksel bölümlerine bağlar. Bu proje için bileşenler, yedi segmentli ekran, dahili 100 mHz saat, orta düğme ve sağ düğme için dört anot ve bunların sekiz katotunun her birini içerir.

Adım 5: Test Et

Kodu tamamladıktan sonra artık FPGA'yı USB kablosu ile programlayabilirsiniz. Yedi segmentli ekran 0.00 göstermelidir. Zamanlayıcıyı 60.00'a ulaşana ve durana kadar başlatmak için ortadaki düğmeye basarak düğmelerin çalışıp çalışmadığını test edin; Arada herhangi bir zamanda, duraklatmak için ortadaki düğmeye tekrar basabilirsiniz. Duraklatıldığında, zamanlayıcıyı tekrar 0,00'a sıfırlamak için sağ düğmeye basabilirsiniz. Her şey doğru çalışıyorsa, tebrikler bir dakikalık bir zamanlayıcı oluşturdunuz!

Önerilen:

Arduino Leonardo Kronometre: 3 Adım

Arduino Leonardo Kronometre: Kredi: https://www.instructables.com/id/Arduino-Stopwatch…Bu kronometre tasarımı, 1'den sayan bir kronometre olan yukarıdaki bağlantıdan kaynaklanmaktadır, oysa bu kronometre 60 saniyeden geri saymaktadır. . Kullandığım kodun çoğu orijinali takip ediyor

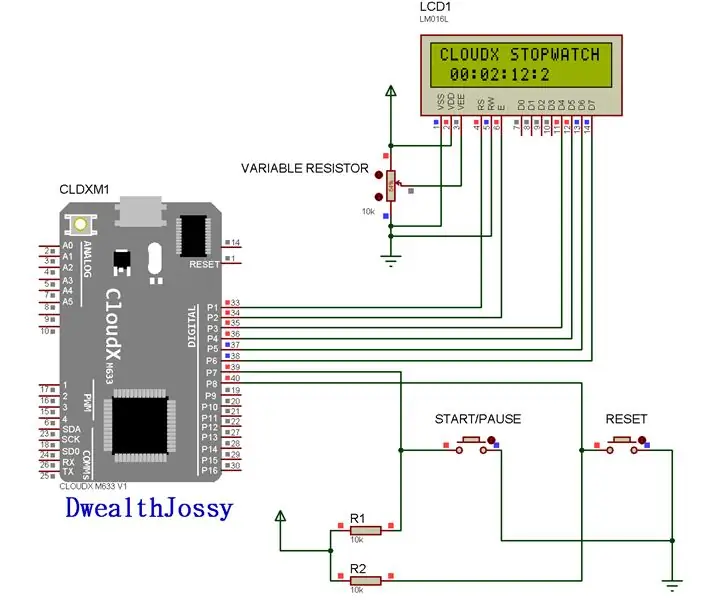

Basit CloudX M633 Dijital Kronometre: 4 Adım

Basit CloudX M633 Dijital Kronometre: Bu projede, cep telefonunuzdaki bir kronometre gibi saat, dakika ve saniye kaydını tutabilen bir dijital saat versiyonu yapacağız! Saati görüntülemek için bir LCD kullanacağız

Hepsi Bir Arada Dijital Kronometre (Saat, Zamanlayıcı, Alarm, Sıcaklık): 10 Adım (Resimli)

Hepsi Bir Arada Dijital Kronometre (Saat, Zamanlayıcı, Alarm, Sıcaklık): Başka bir yarışma için bir Zamanlayıcı yapmayı planlıyorduk, ancak daha sonra bir saat de uyguladık (RTC'siz). Programlamaya başladığımızda, cihaza daha fazla işlevsellik uygulamakla ilgilendik ve sonunda DS3231 RTC'yi ekledik

VHDL ve Basys3 Board Kullanan Temel Kronometre: 9 Adım

VHDL ve Basys3 Board Kullanan Temel Kronometre: Temel VHDL ve Basys 3 board kullanarak bir kronometrenin nasıl oluşturulacağına ilişkin talimata hoş geldiniz. Projemizi sizinle paylaşmaktan heyecan duyuyoruz! Bu, Güz 2016'da Cal Poly, SLO'da CPE 133 (Dijital Tasarım) kursu için bir final projesiydi. İnşa ettiğimiz proje

VHDL Kronometre: 8 Adım (Resimlerle)

VHDL Kronometre: Bu, VHDL ve Basys3 Atrix-7 Board gibi bir FPGA devre kartı kullanarak nasıl kronometre yapılacağına dair bir eğitimdir. Kronometre 00.00 saniyeden 99,99 saniyeye kadar sayabilir. Biri başlat/durdur düğmesi için diğeri de bu düğme için olmak üzere iki düğme kullanır