İçindekiler:

- Yazar John Day day@howwhatproduce.com.

- Public 2024-01-30 13:17.

- Son düzenleme 2025-01-23 15:13.

AmCoderhttps://www.linkedin.com/in/mituFollow tarafından Yazarın daha fazlası:

Hakkında: Mitu Raj -- Sadece Bir Hobi ve Öğrenci -- Çip Tasarımcı -- Yazılım Geliştirici -- Fizik ve Matematik Meraklısı AmCoder Hakkında Daha Fazla Bilgi »

##Bu, sinüs ve kosinüs dalgası oluşturmak için CORDIC ALGORITHM'nin VHDL uygulaması için Google'da en çok tıklanan, popüler bağlantıdır## Şu anda, donanım açısından verimli birçok algoritma mevcuttur, ancak bunlar yazılım sistemlerinin baskınlığı nedeniyle iyi bilinmemektedir. uzun yıllar. CORDIC, belirli trigonometrik, hiperbolik, doğrusal ve logaritmik işlevler dahil olmak üzere çok çeşitli işlevleri hesaplamak için kullanılan bir kaydırma ve toplama mantığı kümesinden başka bir şey olmayan böyle bir algoritmadır. Bu, hesap makinelerinde vb. kullanılan algoritmadır. Bu nedenle, sadece basit kaydırıcılar ve toplayıcılar kullanarak, daha az karmaşıklık, ancak DSP'nin gücü olan bir donanım tasarlayabiliriz. Bu nedenle, VHDL veya Verilog'da herhangi bir özel kayan nokta birimi veya karmaşık matematik IP'leri kullanılmadan çıplak RTL tasarımı olarak tasarlanabilir.

Adım 1: VHDL ve Modelsim

Burada, bir sinüs dalgası ve bir koza dalgası oluşturmak için VHDL kullanılarak kordik algoritma uygulanır. Giriş açısının sinüs ve kosinüsünü büyük bir hassasiyetle verebilir. Kod, FPGA'da sentezlenebilir. Modelsim, tasarımı ve test tezgahını simüle etmek için kullanılır.

Adım 2: Tasarım ve Test Tezgahı için VHDL Kodu

Kayan nokta sayılarını temsil etmek için ikili ölçekleme tekniği kullanılır.

Lütfen kodlamadan önce ekli dokümanları inceleyin.

Cordic_v4.vhd'yi simüle edin - Tasarım -Giriş 32 bitlik açı + işaret bitidir; 0.000000000233 derecelik giriş hassasiyeti ile 0'dan +/-360 dereceye kadar herhangi bir açıyı işleyebilir. Girdi verilirken -> MSB işaret bitidir ve kalan 32 bit büyüklüğü temsil eder.-Tasarımın çıkışı 16 bitlik sinüs ve cos değeri + işaret bitidir.ie; hassas 0.00001526 ile. İlgili sinüs veya cos değeri negatifse, çıktının 2'nin tamamlayıcı formunda görüntülendiğini lütfen unutmayın. Simülasyon testb.vhd - Tasarım için Test Tezgahı (1) Giriş açıları ve çekme sıfırlama ='0'. Simülasyonun iki adımından sonra sıfırlamayı '1'e getirin ve "tümünü çalıştır".(2) Simülasyon penceresinde sin ve cos sinyallerinin yarıçapını ondalık ve format > Analog (otomatik) olarak ayarlayın.(3) Dalga biçimini görmek için uzaklaştırın uygun şekilde.

3. Adım: Eklenen Dosyalar

(1) cordic_v4.vhd - Tasarım.(2) testb.vhd - Tasarım için test tezgahı.

(3) Açı girişlerinin nasıl zorlanacağını ve ikili sonuçların nasıl dönüştürüleceğini belgeleyin.

Güncelleme: BU DOSYALAR ESKİDİR VE ARTIK SAĞLANMAMAKTADIR. LÜTFEN SONRAKİ ADIMDAN DOSYALARI KULLANIN

Adım 4: Mini-Cordic IP Core - 16 Bit

Yukarıdaki uygulamanın sınırlaması, hesaplamaların tek bir saat döngüsünde yapılması nedeniyle yavaş, daha düşük saat çalışma frekansıdır. Mini-Cordic IP Core - 16 Bit

- Performansı artırmak için birden fazla döngüye dağıtılan kritik yollar. - Daha hızlı - 100 Mhz saate kadar sentezlenmiş FPGA kanıtlanmış tasarım. - HDL'de daha fazla alan optimize edilmiş, Daha az donanım. - Yük ve Bitti Durum sinyalleri eklendi. - Tek dezavantajı, daha düşük çözünürlük. önceki bir. Testbench:

0 ila 360 derecelik açı girişleri tamamen otomatik

Ekli Dosyalar:1) mini kordonlu ana vhdl dosyası2) mini kordonlu test tezgahı3) Mini Cordic IP Çekirdek kılavuzu4) Açıların nasıl zorlanacağı ve sonuçların nasıl dönüştürüleceği ile ilgili doküman

Herhangi bir sorunuz için benimle iletişime geçmekten çekinmeyin:

Mitu Raj

beni takip et:

posta: iammituraj@gmail.com

###Toplam indirme: 01-05-2021'e kadar 325###

### Kodda son düzenleme: Temmuz-07-2020 ###

Önerilen:

LCD ile 8051 ve IR Sensör Kullanan Ziyaretçi Sayacı: 3 Adım

LCD ile 8051 ve IR Sensör Kullanan Ziyaretçi Sayacı: Sevgili Arkadaşlar, 8051 ve IR sensör kullanarak ziyaretçi sayacının nasıl yapıldığını anlattım ve LCD'de görüntüledim. 8051, tüm dünyada hobi, ticari uygulamalar yapmak için kullanılan en popüler mikro denetleyicilerden biridir. vizit yaptım

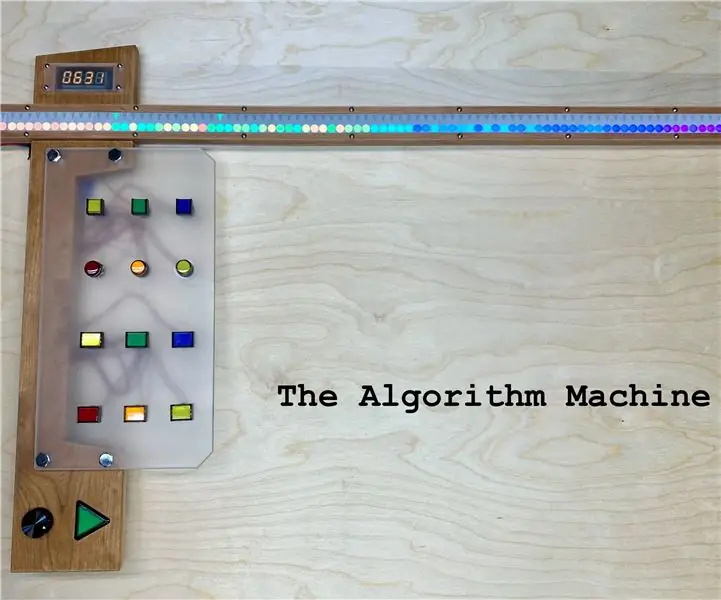

Algoritma Makinesi: 13 Adım (Resimlerle)

Algoritma Makinesi: 15 yıldır üniversite düzeyinde bilgisayar bilimi öğretiyorum ve uzmanlığım daha çok programlama tarafında olsa da, arama ve sıralama için standart algoritmaları ele almak için hala oldukça fazla zaman harcıyorum. Öğretim açısından

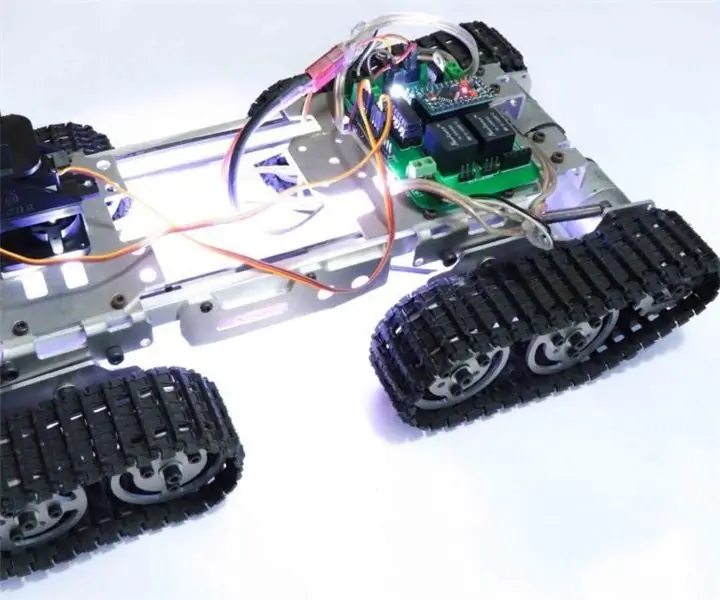

Arduino Kullanan RC Paletli Robot - Adım Adım: 3 Adım

Arduino Kullanan RC Paletli Robot – Adım Adım: Merhaba arkadaşlar, BangGood'tan başka bir harika Robot kasasıyla geri döndüm. Spinel Crux V1 – Hareket Kontrollü Robot, Spinel Crux L2 – Robotik Kollu Arduino Al ve Yerleştir Robotu ve The Badland Braw

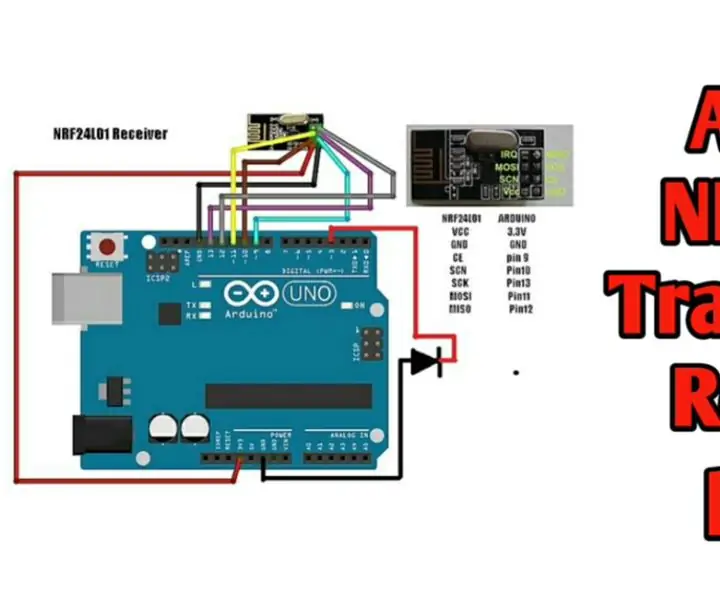

Arduino İle 2.4Ghz NRF24L01 Modülünü Kullanan Kablosuz Uzaktan Kumanda - Nrf24l01 Quadcopter için 4 Kanal / 6 Kanal Verici Alıcı - Rc Helikopter - Arduino Kullanan Rc Uçak: 5 Adım

Arduino İle 2.4Ghz NRF24L01 Modülünü Kullanan Kablosuz Uzaktan Kumanda | Nrf24l01 Quadcopter için 4 Kanal / 6 Kanal Verici Alıcı | Rc Helikopter | Arduino Kullanan Rc Uçak: Bir Rc araba çalıştırmak için | Quadcopter | dron | RC uçak | RC tekne, her zaman bir alıcı ve vericiye ihtiyacımız var, RC QUADCOPTER için 6 kanallı bir verici ve alıcıya ihtiyacımız olduğunu ve bu tür TX ve RX'in çok maliyetli olduğunu varsayalım, bu yüzden bir tane yapacağız

VHDL ve Basys3 Board Kullanan Temel Kronometre: 9 Adım

VHDL ve Basys3 Board Kullanan Temel Kronometre: Temel VHDL ve Basys 3 board kullanarak bir kronometrenin nasıl oluşturulacağına ilişkin talimata hoş geldiniz. Projemizi sizinle paylaşmaktan heyecan duyuyoruz! Bu, Güz 2016'da Cal Poly, SLO'da CPE 133 (Dijital Tasarım) kursu için bir final projesiydi. İnşa ettiğimiz proje