İçindekiler:

- Yazar John Day day@howwhatproduce.com.

- Public 2024-01-30 13:19.

- Son düzenleme 2025-01-23 15:13.

Bu talimatta, RTL'de basit bir VGA Denetleyici tasarlayacağız. VGA Denetleyici, VGA ekranlarını çalıştırmak için tasarlanmış dijital devredir. Görüntülenecek çerçeveyi temsil eden Çerçeve Arabelleğinden (VGA Belleği) okur ve görüntüleme amacıyla gerekli verileri ve senkronizasyon sinyallerini üretir.

Verilog/System verilog kodunu arıyorsanız: Verilog'daki VGA Controller and Video System blogumu ziyaret edin

Adım 1: VGA Denetleyici Arayüzü

Aşağıdakiler, bir VGA Denetleyicisindeki ana arayüz sinyalleridir.

- Piksel Saat veya VGA Saat

- HSYNC ve VSYNC sinyalleri

Seçilen VGA ekranı için, önce onu sürmek için gereken Pixel Clock frekansını hesaplamanız gerekir. 3 parametreye bağlıdır: Toplam Yatay Piksel, Toplam Dikey Piksel, Ekran Yenileme Hızı.

Tipik olarak, F = THP * TVP * Yenileme Hızı

Ekli RAR'da çeşitli VGA ekranlar için gereken piksel saati ile ilgili belgeleri bulun.

HSYNC ve VSYNC sinyalleri Pixel saatinden üretilir. HSYNC ve VSYNC sinyallerinin zamanlaması parametre sayısına bağlıdır: Yatay ve Dikey Ön Kapı, Yatay ve Dikey Arka Kapı, Yatay ve Dikey Ekran Pikselleri, Yatay ve Dikey Senkron Darbe Genişlikleri ve Kutupları.

Bu parametreler, seçilen bir VGA ekranı için standartlaştırılmıştır. Bu belgeleri ekteki RAR'da bulun.

Bu parametreler, VGA Denetleyici IP'mizde yapılandırılabilir parametrelerdir.

2. Adım: VGA Denetleyiciyi VGA Ekranla Entegre Etme

Şekil, VGA Denetleyicinin bir VGA ekranıyla nasıl entegre edileceğini gösterir. Sistemi tamamlamak için iki bileşene daha ihtiyacınız var:

- Çerçeve Tamponu: Görüntülenecek çerçeveyi tutan bellek.

- Video DAC: RGB dijital verilerini dönüştüren ve VGA Ekranını uygun voltaj seviyesinde RGB analog sinyalleriyle çalıştıran DAC.

En basit ve popüler Video DAC'lerden biri ADV7125'tir. RGB dijital kelimeleri 0-0,7 V analog sinyallere dönüştüren ve VGA ekranını çalıştıran 8 bitlik bir DAC'dir.

Adım 3: Çerçeve Tampon Tasarımı

Görüntülenecek görüntüyü 'saklayan' bellektir. Genellikle bir RAM veya bazen ROM'dur. Bir görüntüyü temsil etmek için bir çerçeve arabelleğinin nasıl tasarlanacağını tartışacağız. Çerçeve arabelleği, bu dijital bilgiyi VGA Denetleyiciden gelen bir Video DAC açık komutuna iletir.

Öncelikle gerekli piksel derinliğine karar vermeliyiz. Görüntünün kalitesine, bir pikselin temsil edebileceği renk çeşitliliğine karar verir. 8 bitlik bir DAC için, bir pikselin birincil renk bileşenlerini temsil etmemiz gerekir: R, G ve B'nin her biri 8 bit. Bu, bir pikselin 24 bit olduğu anlamına gelir.

Her piksel, Frame Buffer bellek konumlarında bitişik bir şekilde depolanır.

Gösterilecek bir görüntünün 800x600 piksel olduğunu varsayalım.

Bu nedenle gerekli olan Çerçeve Arabelleği 800x600 = 480000 x 24 bit bellektir

Belleğin toplam boyutu yaklaşık 800x600x24 = 1400 kB'dir.

Siyah beyaz görüntü ise, 800x600x1 = 60 kB yakl.

Blok RAM'ler, Xilinx FPGA'larda bir Çerçeve Tamponunu temsil etmek için kullanılabilir.

4. Adım: Notlar

- Seçilen DAC'ye bağlı olarak VGA Denetleyicide ek sinyaller gerekir. ADV7125 kullandım.

- VGA ekranını çalıştırmadan önce VSYNC ve HSYNC'de parmak arası terlikler aracılığıyla döngü gecikmeleri ekleyin. Bunun nedeni DAC ve Bellek gecikmeleridir. Piksel sinyalleri HSYNC ve VSYNC ile senkronize edilmelidir. Benim durumumda 2 döngü gecikmesi oldu.

- Belirtilen boyuttaki Çerçeve Tamponu blok ram boyutu sınırlaması nedeniyle FPGA'da tasarlanamıyorsa, görüntüyü temsil etmek için daha küçük bellek kullanın ve tam çerçeve sınırı yerine kullanılabilir belleğin sınırındaki adresin üzerinden geçmek için kodu düzenleyin. Bu, aynı görüntüyü tüm ekran boyunca tekrar tekrar çoğaltacaktır. Diğer bir yöntem, tüm görüntüyü daha düşük bir çözünürlükte tam ekranda göstermek için her pikselin çoğaltıldığı piksel ölçeklendirmedir. Bu, koddaki adres artış mantığını değiştirerek yapılabilir.

- IP, tüm FPGA'larda tamamen taşınabilirdir ve Virtex-4 FPGA'da 100 MHz'e kadar zamanlama doğrulanmıştır.

Adım 5: Ekli Dosyalar

RAR şunları içerir:

- VGA Denetleyici kodu

- VGA standartlarının PDF'leri.

Önerilen:

VHDL'de Basit Dört Yönlü Küme İlişkili Önbellek Denetleyicisi Tasarımı: 4 Adım

VHDL'de Basit Dört Yollu Set İlişkili Önbellek Denetleyicisinin Tasarımı: Önceki talimatımda, basit bir doğrudan eşlenmiş önbellek denetleyicisinin nasıl tasarlanacağını gördük. Bu sefer bir adım ileri gidiyoruz. Basit bir dört yollu küme ilişkisel önbellek denetleyicisi tasarlayacağız. Avantaj? Daha az kayıp oranı, ancak performans pahasına

VHDL'de Programlanabilir Kesinti Denetleyicisi Tasarımı: 4 Adım

VHDL'de Programlanabilir Kesinti Denetleyicisi Tasarımı: Bu blogda aldığım yanıtlardan çok etkilendim. Arkadaşlar, blogumu ziyaret ettiğiniz ve bilgilerimi sizinle paylaşmam için beni motive ettiğiniz için teşekkür ederim. Bu sefer, tüm SOC'lerde gördüğümüz başka bir ilginç modülün tasarımını sunacağım -- Interrupt C

VHDL'de Basit Bir Önbellek Denetleyicisi Tasarımı: 4 Adım

VHDL'de Basit Bir Önbellek Denetleyicisinin Tasarımı: Bu talimatı yazıyorum, çünkü bir önbellek denetleyicisi tasarlamaya başlamak ve öğrenmek için bazı referans VHDL kodunu almayı biraz zor buldum. Bu yüzden kendim sıfırdan bir önbellek denetleyicisi tasarladım ve FPGA üzerinde başarıyla test ettim. bende p

Basit ve Kolay Adımlarla PCB Tasarımı: 30 Adım (Resimlerle)

Basit ve Kolay Adımlarla PCB Tasarımı: MERHABA ARKADAŞLAR PCB tasarımını öğrenmek isteyenler için çok kullanışlı ve kolay öğretici, hadi başlayalım

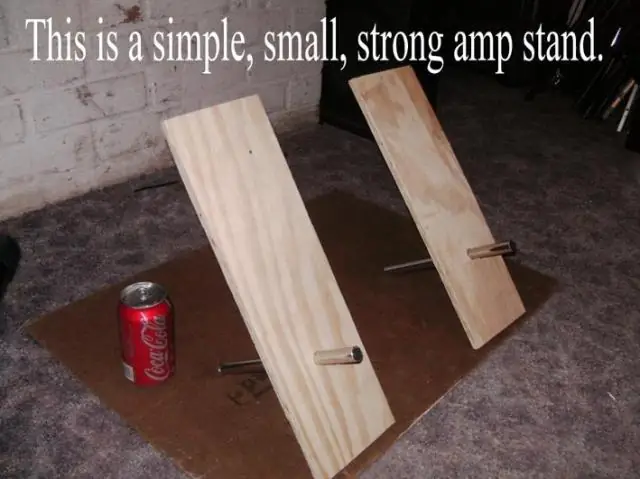

Gitar Amfi Tilt Standı - "Afrika Sandalye" Tasarımı - Basit, Küçük, Güçlü, Kolay, Ücretsiz veya Gerçek Ucuz: 9 Adım

Guitar Amp Tilt Stand - "African Chair" Tasarım - Basit, Küçük, Güçlü, Kolay, Ücretsiz veya Gerçek Ucuz: Gitar Amp Tilt Standı - Çok Kolay - basit, küçük, güçlü, ücretsiz veya gerçekten ucuz. Tüm boyutlardaki amfiler için, hatta ayrı başlıklı büyük dolaplar için. Sadece panoları ve boruları istediğiniz boyutta yapın ve istediğiniz hemen hemen her ekipmana ihtiyacınız var