İçindekiler:

- Adım 1: Vivado HLS Nedir?

- 2. Adım: HLS Video Kitaplığı

- 3. Adım: Sentezleme

- 4. Adım: Versiyon Oluşturma ve Dışa Aktarma için Diğer Bilgiler

- Adım 5: Vivado IP Kitaplığına Aktarma

- Adım 6: Sentez ve Dışa Aktarma Analizi

- 7. Adım: Vivado'da IP Kitaplığı Ekleme

- 8. Adım: Yükseltme Yapma

- 9. Adım: Ek Ayrıntılar ve Bilgiler

- Adım 10: Çıktı ve Girdi

- Adım 11: AXI Kayıt Arabirimi

- Adım 12: Veri Akışı Pragması

- Yazar John Day day@howwhatproduce.com.

- Public 2024-01-30 13:21.

- Son düzenleme 2025-01-23 15:14.

Hiç gecikme eklemeden veya gömülü bir sistemde video üzerinde gerçek zamanlı işleme yapmak istediniz mi? FPGA'lar (Alan Programlanabilir Kapı Dizileri) bazen bunu yapmak için kullanılır; ancak video işleme algoritmalarını VHDL veya Verilog gibi donanım spesifikasyon dillerinde yazmak en iyi ihtimalle sinir bozucu. C++ ortamında programlamanıza ve ondan donanım spesifikasyon dil kodu oluşturmanıza izin veren Xilinx aracı olan Vivado HLS'ye girin.

Gerekli yazılımlar:

- Vivado HLS

- canlı

- (AXI kayıtlarını kullanıyorsanız) Vivado SDK

(İsteğe bağlı) Xilinx yapımı örnekleri buradan indirin:

Xilinx HLS video örnekleri

Adım 1: Vivado HLS Nedir?

Vivado HLS, c++ benzeri kodu bir FPGA üzerinde uygulanabilen donanım yapılarına dönüştürmek için kullanılan bir araçtır. Bu geliştirmeyi yapmak için bir IDE içerir. HLS için kod geliştirmenizi tamamladıktan sonra, oluşturulan IP'nizi bir formatta dışa aktarabilirsiniz. Vivado ile kullanım için.

Ekli dosyaları indirin ve projenizi oluşturacağınız yere yakın bir yere koyun. (rastgele bir adları varsa, bunları "top.cpp" ve "top.h" olarak yeniden adlandırın)

2. Adım: HLS Video Kitaplığı

HLS Video Kitaplığı, bu belgede referans tasarımlarıyla belgelere sahiptir:XAPP1167Bir başka iyi kaynak da bununla ilgili Xilinx Wiki sayfasıdır.

Vivado HLS'yi başlatın.

Yeni bir proje oluşturun.

Bir önceki adımda indirdiğiniz dosyaları alın ve kaynak dosya olarak ekleyin. (Not: dosyalar projeye kopyalanmaz, bunun yerine oldukları yerde kalırlar)

Ardından en üstteki işlevi seçmek için Gözat düğmesini kullanın.

Bir sonraki sayfada, kullandığınız Xilinx parçasını seçin.

3. Adım: Sentezleme

Çözüm => C Sentezini Çalıştır => Etkin Çözüm

~227.218 saniye sonra yapılmalıdır. (Not: gerçek sentez süreniz birçok faktöre bağlı olarak değişecektir)

4. Adım: Versiyon Oluşturma ve Dışa Aktarma için Diğer Bilgiler

Sürüm numaraları, bir tasarımdaki IP'yi güncelleyebilmeniz için Vivado ile etkileşime girer. Küçük bir sürüm değişikliği ise, büyük sürüm değişiklikleri yeni bloğu manuel olarak eklemenizi ve eskisini kaldırmanızı gerektirirken yerinde yapılabilir. Arayüzleriniz değişmediyse ve sürüm güncellemesi küçükse, güncelleme yapılabilir. IP güncelleme düğmesine basarak tamamen otomatik olarak yapılır. IP'nizin durumunu görmek için Vivado tcl konsolunda "report_ip_status" çalıştırabilirsiniz.

Sürüm numaralarını ve diğer bilgileri Çözüm => Çözüm Ayarları'nda ayarlayın…

Alternatif olarak, bu ayarlar dışa aktarma sırasında ayarlanabilir.

Adım 5: Vivado IP Kitaplığına Aktarma

Çözüm => RTL'yi dışa aktar

IP kitaplığı ayrıntılarını önceki adımda ayarlamadıysanız, bunu şimdi yapabilirsiniz.

Adım 6: Sentez ve Dışa Aktarma Analizi

Bu ekranda, dışa aktarılan modülümüzün 10ns (100MHz) saat periyodumuzu karşıladığını ve her kaynağın ne kadarını kullandığını gösteren istatistikleri görebiliriz.

Bunun, Sentez Raporumuz ve Veri Akışı analizimizin birleşimiyle, 317338 saat döngüsü * 10ns saat periyodu * 14 ardışık düzen aşaması = 0.04442732 saniye sürdüğünü görebiliriz. Bu, görüntü işlememiz tarafından eklenen toplam gecikmenin saniyenin yirmide birinden daha az olduğu anlamına gelir (hedeflenen 100 MHz'de saat hızı ayarlandığında).

7. Adım: Vivado'da IP Kitaplığı Ekleme

Sentezlenmiş IP bloğunuzu kullanmak için onu Vivado'ya eklemeniz gerekecek.

Vivado'da IP kataloğuna gidip "Depo Ekle…" seçeneğini seçerek projenize bir IP deposu ekleyin.

Vivado HLS proje dizininize gidin ve çözüm dizininizi seçin.

Bulduğu IP'yi rapor etmelidir.

8. Adım: Yükseltme Yapma

Bazen bir Vivado tasarımına dahil ettikten sonra HLS bloğunuzda değişiklik yapmanız gerekir.

Bunu yapmak için, değişiklikleri yapabilir ve IP'yi yeniden sentezleyebilir ve daha yüksek bir sürüm numarasıyla dışa aktarabilirsiniz (ana/küçük sürüm numarası değişiklikleriyle ilgili önceki adımdaki ayrıntılara bakın).

Yeni sürümü dışa aktarmayı değiştirdikten sonra, Vivado'daki IP depolarınızı yenileyin. Bu, Vivado IP'nin depoda değiştiğini fark ettiğinde veya manuel olarak etkinleştirildiğinde yapılabilir. (Başladıktan sonra, ancak HLS'de dışa aktarma tamamlanmadan önce IP depolarınızı yenilerseniz, IP'nin geçici olarak orada olmayacağını, bitmesini bekleyin ve yeniden yenilenmesini bekleyin.)

Bu noktada, diskte bir IP'nin değiştirildiği bilgisini içeren bir pencere görünmelidir ve size "Seçili Yükselt" düğmesi ile güncelleme seçeneği sunar. Değişiklik küçük bir sürüm değişikliğiyse ve arayüzlerin hiçbiri değişmediyse, daha sonra bu düğmeye basmak, eski IP'yi otomatik olarak yenisiyle değiştirir, aksi takdirde daha fazla çalışma gerekebilir.

9. Adım: Ek Ayrıntılar ve Bilgiler

Aşağıdaki adımlar, HLS sentezinin nasıl çalıştığı ve bununla neler yapabileceğiniz hakkında daha fazla bilgi sağlar.

HLS sentezlenmiş bir IP bloğu kullanan bir proje örneği için bu talimata bakın.

Adım 10: Çıktı ve Girdi

Son IP bloğunun çıktıları ve girdileri, üst fonksiyona giren ve çıkan veri akışının sentezleyicinin yaptığı bir analizden belirlenir.

VHDL veya verilog'a benzer şekilde, HLS, IP arasındaki bağlantılarla ilgili ayrıntıları belirlemenize olanak tanır. Bu satırlar buna örnektir:

void image_filter(AXI_STREAM& video_in, AXI_STREAM& video_out, int& x, int&y) {

#pragma HLS INTERFACE eksen bağlantı noktası=video_in package=INPUT_STREAM #pragma HLS INTERFACE eksen bağlantı noktası=video_out package=OUTPUT_STREAM #pragma HLS INTERFACE s_axilite bağlantı noktası=x paket=CONTROL_BUS ofseti=0x14#pragma HLS INTERFACE bağlantı noktası_=ya paket

IP bloğunda sergilenen portların bu direktiflerden nasıl etkilendiğini görebilirsiniz.

Adım 11: AXI Kayıt Arabirimi

IP bloğunuzdan PS'ye giriş/çıkış almak için bunu yapmanın iyi bir yolu bir AXI arabirimidir.

Bunu, değere daha sonra erişmek için kullanılacak ofsetler de dahil olmak üzere, HLS kodunuzda şu şekilde belirtebilirsiniz:

void image_filter(AXI_STREAM& video_in, AXI_STREAM& video_out, int& x, int&y) {

#pragma HLS INTERFACE s_axilite bağlantı noktası=x paket=CONTROL_BUS offset=0x14

#pragma HLS INTERFACE s_axilite bağlantı noktası=y paket=CONTROL_BUS offset=0x1C #pragma HLS veri akışı

x = 42;

y = 0xDEADBEEF; }

Vivado'ya düzgün bir şekilde bağlandıktan sonra, Vivado SDK'da bu kodu kullanarak değerlere erişebilirsiniz:

#include "parameters.h"

#define xregoff 0x14 #define yregoff 0x1c x = Xil_In32(XPAR_IMAGE_FILTER_0_S_AXI_CONTROL_BUS_BASEADDR+xregoff); y = Xil_In32(XPAR_IMAGE_FILTER_0_S_AXI_CONTROL_BUS_BASEADDR+yregoff);

Bu, x'te 42 ve y'de 0xdeadbeef ile sonuçlanmanızı sağlayacaktır.

Adım 12: Veri Akışı Pragması

#pragma DATAFLOW içinde, kodun uygulanma şekli normal C++'dan değişir. Kod, tüm talimatların her zaman verilerin farklı bölümlerinde çalışacak şekilde ardışık düzene sahiptir (Bunu bir fabrikadaki montaj hattı gibi düşünün, her istasyon sürekli çalışıyor ve bir işlevi yerine getiriyor ve bir sonraki istasyona geçiyor)

resimden, direktiflerin her birinin

Normal değişkenler gibi görünse de, img nesneleri aslında komutlar arasında küçük arabellekler olarak uygulanır. Bir işlevin girdisi olarak bir görüntüyü kullanmak, onu "tüketir" ve artık kullanılamaz hale getirir. (Dolayısıyla yinelenen komutlara duyulan ihtiyaç)

Önerilen:

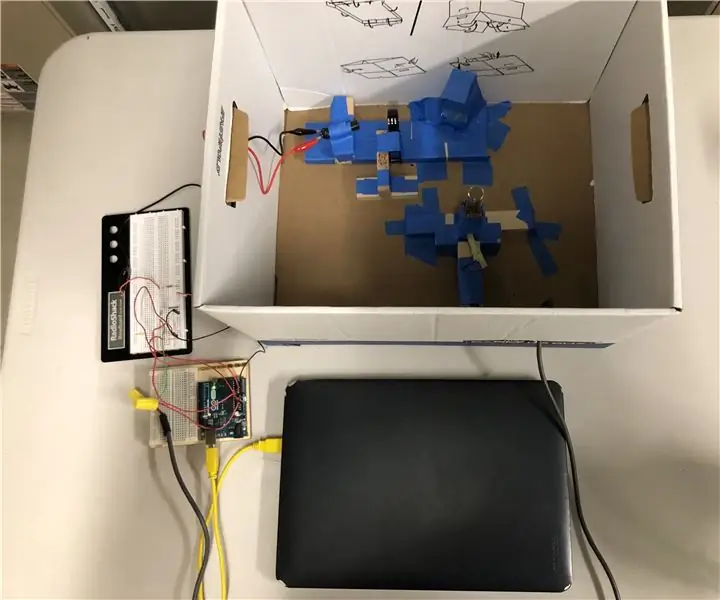

Yosun Deneyleri için Ev Yapımı Jenga Blok Spektrofotometresi: 15 Adım

Yosun Deneyleri için Ev Yapımı Jenga Blok Spektrofotometresi: Algler fotosentetik protistlerdir ve bu nedenle suda yaşayan besin zincirlerinde kritik organizmalardır. Ancak ilkbahar ve yaz aylarında bu ve diğer mikroorganizmalar çoğalabilir ve doğal su kaynaklarını tüketerek oksijen tükenmesine neden olabilir

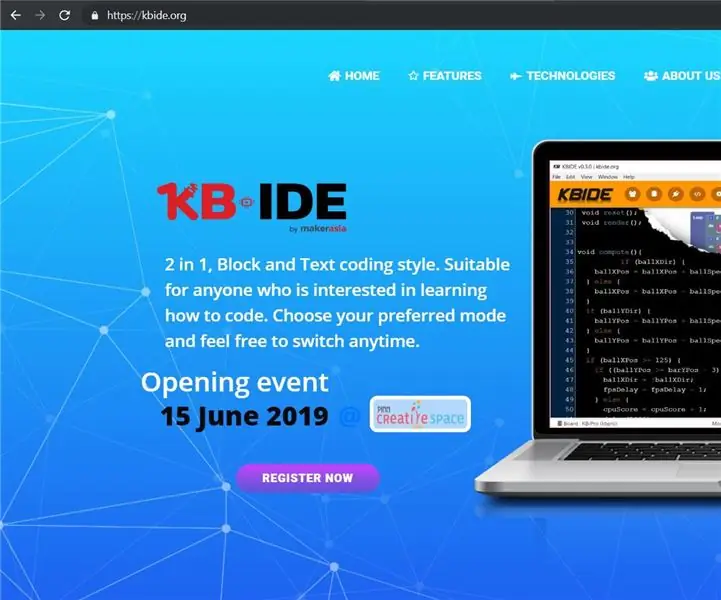

KB-IDE: ESP32 Board için Blok Programı: 5 Adım

KB-IDE: ESP32 Board için Blok Programı: 15 Haziran 2019'da MakerAsia, ESP-IDF ve Arduino IDE (ESP32 Core) için yeni IDE olan KB-IDE'yi piyasaya sürdü.KB-IDE, IoT panoları için üçlü mod programlama IDE'sidir. Şu anda ESP32 kartlarını desteklemektedir. Kullanıcılar Blok modunda (Görsel programlama) ve Kod

Retro Konuşma Sentezi. Bölüm: 12 IoT, Ev Otomasyonu: 12 Adım (Resimlerle)

Retro Konuşma Sentezi. Bölüm: 12 IoT, Ev Otomasyonu: Bu makale, bir IoT Retro Konuşma Sentez Cihazının nasıl oluşturulacağını ve mevcut bir ev otomasyon sistemine nasıl entegre edileceğini belgeleyen ev otomasyonu Talimatları serisinin 12.'sidir

Vivado Simluation Nasıl Kullanılır: 6 Adım

Vivado Simluation Nasıl Kullanılır: Bu simülasyon projesini online bir ders için yaptım. Proje Verilog tarafından yazılmıştır. Daha önce oluşturulmuş kronometre projesindeki dalga biçimini enable_sr(enable digit) içinde görselleştirmek için Vivado'da simülasyonu kullanacağız. Ayrıca, yapacağımız

Bilgisayarınızda Analog Ses Sentezi: 10 Adım (Resimlerle)

Bilgisayarınızdaki Analog Ses Sentezi: Eski analog sentezleyicilerin sesi gibi mi? Biriyle istediğiniz zaman, kendi yerinizde, istediğiniz kadar ÜCRETSİZ oynamak ister misiniz? İşte en çılgın Moog hayallerinizin gerçekleştiği yer. Elektronik kayıt sanatçısı veya profesyonel olabilirsiniz