İçindekiler:

- Adım 1: Kaynakları Ekle ve Simülasyon Kaynakları Ekle veya Oluştur'u seçin

- 2. Adım: Enable_sr_tb Adlı Dosyayı Oluşturun

- Adım 3: Testbench Dosyası Oluşturun

- Adım 4: Enable_sr_tb'yi Simülasyon Altında En Üst Düzey Olarak Ayarlayın

- Adım 5: Sentez ve Davranış Simülasyonunu Çalıştırın

- Adım 6: Simülasyon Sonucunu Değerlendirin

- Yazar John Day day@howwhatproduce.com.

- Public 2024-01-30 13:20.

- Son düzenleme 2025-01-23 15:13.

Bu simülasyon projesini çevrimiçi bir sınıf için yaptım. Proje Verilog tarafından yazılmıştır. Daha önce oluşturulmuş kronometre projesinden dalga biçimini enable_sr(enable digit) içinde görselleştirmek için Vivado'da simülasyonu kullanacağız. Ayrıca tasarımda tarafımızca yapılan hatayı görüntülemek için sistem görevini kullanacağız.

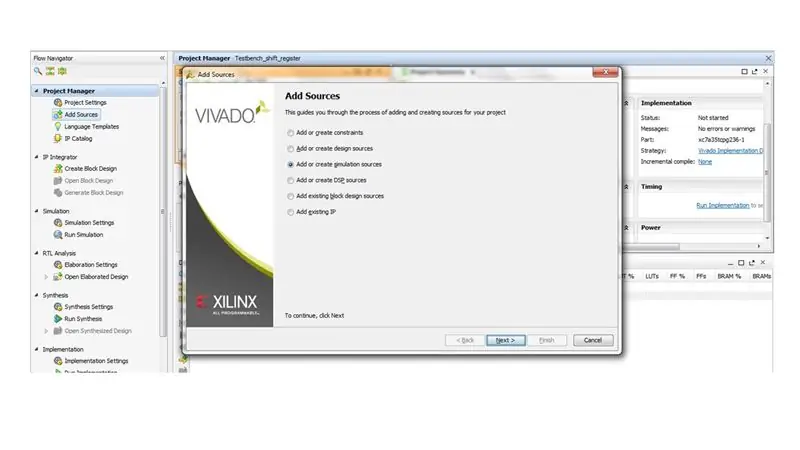

Adım 1: Kaynakları Ekle ve Simülasyon Kaynakları Ekle veya Oluştur'u seçin

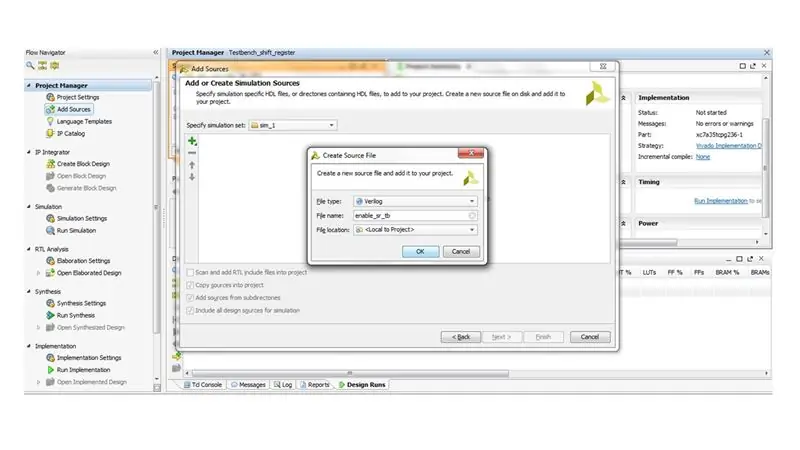

2. Adım: Enable_sr_tb Adlı Dosyayı Oluşturun

Adım 3: Testbench Dosyası Oluşturun

1. Enable_sr modülünü stop watch projesinden içe aktarın. Simüle etmek istediğimiz dosya bu

2. Testbench modülü etkinleştirin_sr_tb() oluşturun;

3. Enable_sr() modülünün giriş ve çıkışlarını girin. Çıkışlar net tip olurken, enable_sr için girişlerin artık register tipinde olduğunu unutmayın.

4. Enable_sr olan test edilen birimi (uut) somutlaştırın

5. Periyodu (T) 20ns olan saati oluşturun

6. Hata kontrol sistemi oluşturmak için koşullu ifadeyi kullanın. Bu örnekte, birden fazla hanenin aktif olup olmadığını kontrol etmek istiyoruz.

Not: Orijinal enable_sr() dosyasında, deseni 4'b0011 olarak başlatmalıyız, böylece hata oluşturmak için iki basamak aktif olur

7. Hatayı göstermek için sistem görevi $display'i kullanın

8. Simülasyonu 400ns zamanında tamamlamak için sistem görevi $finish'i kullanın

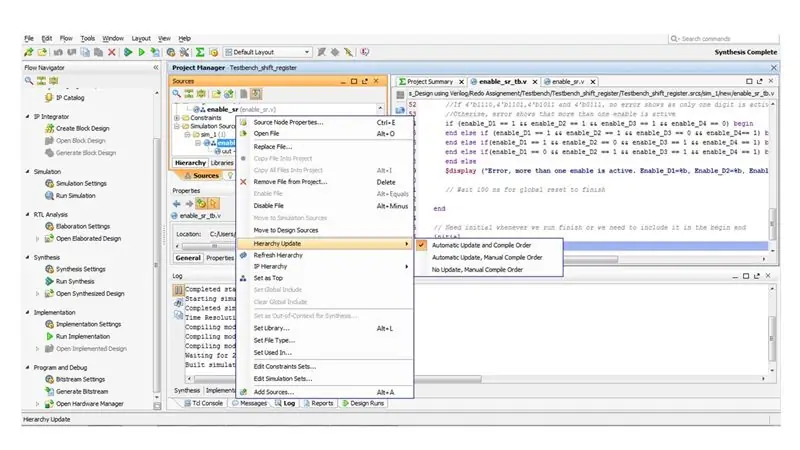

Adım 4: Enable_sr_tb'yi Simülasyon Altında En Üst Düzey Olarak Ayarlayın

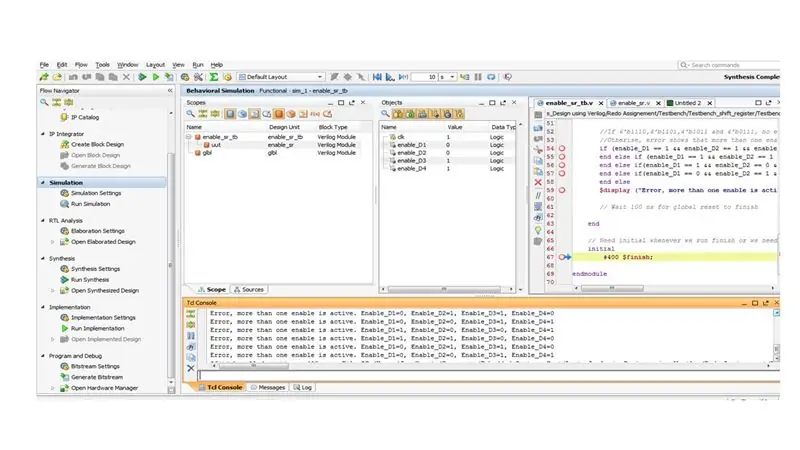

Adım 5: Sentez ve Davranış Simülasyonunu Çalıştırın

- Davranış simülasyonunu çalıştırmadan önce, testbench dosyasında ve test dosyası altındaki ünitede herhangi bir sözdizimi hatası olmadığından emin olmak için sentezi çalıştırın.

- Davranış simülasyonunu çalıştırın

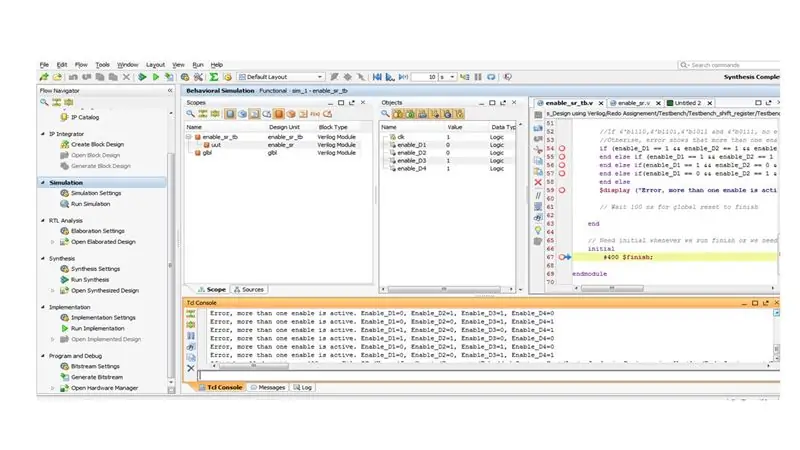

Adım 6: Simülasyon Sonucunu Değerlendirin

Simülasyon pencerelerini göreceksiniz. Farklı paneller içerir.

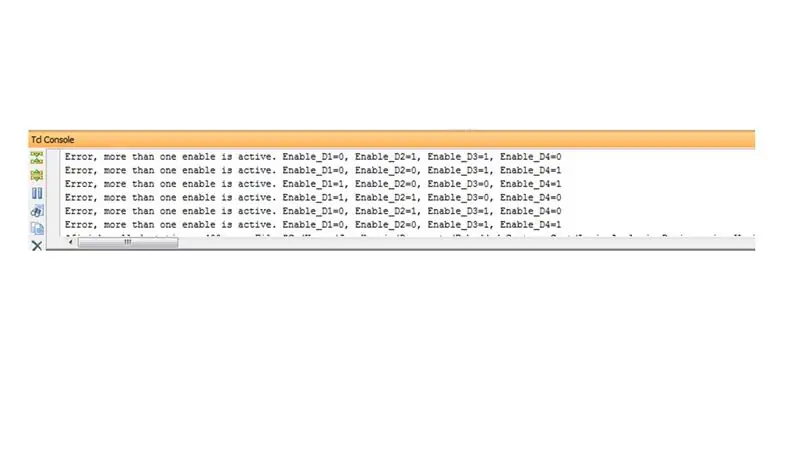

Konsol panelinde hata mesajını göreceksiniz. Bu, simülasyon süresi boyunca birden fazla hanenin aktif olduğunu gösterir.

Kapsamda dalga biçimini de görebilirsiniz.

Proje dosyası ektedir.

Önerilen:

Visuino Bir LED'in Parlaklığını Değiştirmek için Darbe Genişlik Modülasyonu (PWM) Nasıl Kullanılır: 7 Adım

Visuino Bir LED'in Parlaklığını Değiştirmek için Darbe Genişlik Modülasyonu (PWM) Nasıl Kullanılır: Bu eğitimde, Darbe Genişlik Modülasyonu (PWM) kullanarak parlaklığını değiştirmek için Arduino UNO ve Visuino'ya bağlı bir LED kullanacağız. Bir tanıtım videosunu izleyin

Arduino 1.3 İnç OLED Ekran Nasıl Kullanılır SH1106: 7 Adım

Arduino 1.3 İnç OLED Ekran SH1106 Nasıl Kullanılır: Bu dersimizde 1.3 İnç OLED Ekran SH1106 Arduino ve Visuino yazılımının nasıl kullanılacağını öğreneceğiz.Videoyu İzle

Linux Önyükleme Sürücüsü Nasıl Oluşturulur (ve Nasıl Kullanılır): 10 Adım

Bir Linux Önyükleme Sürücüsü Nasıl Oluşturulur (ve Nasıl Kullanılır): Bu, Linux'a, özellikle Ubuntu'ya nasıl başlayacağınızla ilgili basit bir giriştir

Rotary Encoder: Nasıl Çalışır ve Arduino İle Nasıl Kullanılır: 7 Adım

Döner Kodlayıcı: Nasıl Çalışır ve Arduino ile Nasıl Kullanılır: Bu ve diğer harika öğreticileri ElectroPeak'in resmi web sitesinde okuyabilirsinizGenel BakışBu eğitimde, döner kodlayıcıyı nasıl kullanacağınızı öğreneceksiniz. İlk olarak, rotasyonel kodlayıcı hakkında bazı bilgiler göreceksiniz ve ardından nasıl yapılacağını öğreneceksiniz

Mac Terminal Nasıl Kullanılır ve Temel İşlevler Nasıl Kullanılır: 4 Adım

Mac Terminali Nasıl Kullanılır ve Temel Fonksiyonlar Nasıl Kullanılır: Size MAC Terminalini nasıl açacağınızı göstereceğiz. Ayrıca size Terminal içinde ifconfig, dizinleri değiştirme, dosyalara erişim ve arp gibi birkaç özelliği göstereceğiz. Ifconfig, IP adresinizi ve MAC reklamınızı kontrol etmenizi sağlar