İçindekiler:

- Yazar John Day day@howwhatproduce.com.

- Public 2024-01-30 13:20.

- Son düzenleme 2025-01-23 15:13.

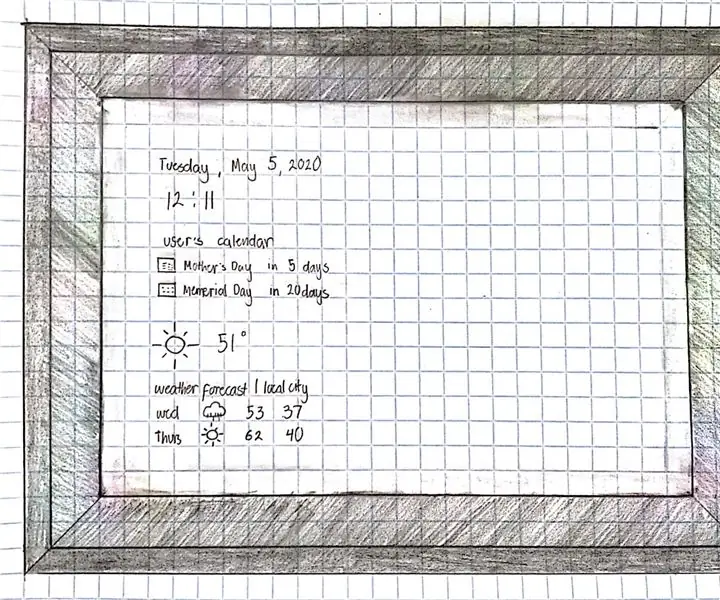

Bu projenin amacı, bir Akıllı Aynanın görüntü görüntüleme işlevselliğini yaratmaktır. Ayna, tahminleri (güneşli, parçalı güneşli, bulutlu, rüzgarlı, yağmur, gök gürültüsü ve kar) ve -9999° ile 9999° arasındaki sıcaklık değerlerini görüntüleyebilir. Tahmin ve sıcaklık değerleri, bir hava durumu API'sinden ayrıştırılmalarını taklit etmek için sabit kodlanmıştır.

Proje, FreeRTOS çalıştıran bir Zynq-Zybo-7000 kartı kullanıyor ve donanımı tasarlamak ve programlamak için Vivado 2018.2 kullanıyor.

Parçalar:

Zynq-Zybo-7000 (FreeRTOS ile)

19 LCD (640x480)

VGA kablosu

12" x 18" akrilik ayna

1. Adım: Vivado'yu Yapılandırma

Xilinx'ten Vivado 2018.2'yi indirin ve Webpack lisansını kullanın. Vivado ve "Create New Project"i başlatın ve ona bir isim verin. Ardından "RTL Projesi"ni seçin ve "Şu anda kaynakları belirtme" seçeneğini işaretleyin. Bir parça seçerken, "xc7z010clg400-1" öğesini seçin ve sonraki sayfada "Son" düğmesine basın.

2. Adım: VGA Sürücüsü IP'sini Paketleme

vga_driver.sv dosyasını Tasarım Kaynaklarına ekleyin. Ardından, "Araçlar"ı tıklayın ve "Yeni IP Oluştur ve Paketle"yi seçin. "Mevcut projenizi paketleyin"i seçin. Ardından bir IP konumu seçin ve ".xci dosyalarını dahil edin". Açılır pencerede "Tamam" ı ve ardından "Son" u tıklayın.

"Paketleme Adımları"nda "İnceleme ve Paketleme"ye gidin ve "IP Paketi"ni seçin.

Şimdi vga_driver bir IP bloğu olarak mevcut olmalıdır.

3. Adım: Zynq IP

"IP Entegratörü" bölümünün altında "Blok Tasarımı Oluştur"u seçin. "ZYNQ7 İşleme Sistemini" ekleyin ve bloğa çift tıklayın. "XPS Ayarlarını İçe Aktar"ı tıklayın ve ZYBO_zynq_def.xml dosyasını yükleyin.

Ardından, "PS-PL Yapılandırması" altında "AXI Güvenli Olmayan Etkinleştirme" açılır menüsünü açın ve "M AXI GP0 arabirimi"ni işaretleyin.

Ardından, "MIO Konfigürasyonu" altında, "Uygulama İşlemci Birimi" açılır menüsünü açın ve "Zamanlayıcı 0" ve "İzleyici"yi kontrol edin.

Son olarak, "Saat Konfigürasyonu" altında "PL Yapı Saatler" açılır menüsünü açın ve "FCLK_CLK0" ve 100 MHz'de kontrol edin.

Adım 4: GPIO IP

Blok Tasarımına iki GPIO bloğu ekleyin. GPIO'lar, piksel adresini ve piksellerin RGB bileşenlerini kontrol etmek için kullanılacaktır. Blokları yukarıdaki resimlerde gösterildiği gibi yapılandırın. Her iki bloğu da ekleyip yapılandırdıktan sonra "Bağlantı Otomasyonunu Çalıştır" ı tıklayın.

GPIO 0 - Kanal 1 piksel adresini kontrol eder ve Kanal 2 kırmızı rengi kontrol eder.

GPIO 1 - Kanal 1 yeşil rengi kontrol eder ve Kanal 2 mavi rengi kontrol eder.

Adım 5: Belleği Engelle

Blok Tasarımına bir Blok Bellek Oluşturucu IP ekleyin ve yukarıda gösterildiği gibi yapılandırın. Piksel renkleri, daha sonra VGA sürücüsü tarafından okunan bellek adreslerine yazılır. Adres satırının kullanılan piksel miktarıyla eşleşmesi gerekir, bu nedenle 16 bit olması gerekir. 16 renk biti olduğu için içindeki veriler de 16 bittir. Herhangi bir onay bitini okumakla ilgilenmiyoruz.

6. Adım: Diğer IP

Ekli pdf, tamamlanmış Blok Tasarımını göstermektedir. Eksik IP'yi ekleyin ve bağlantıları tamamlayın. Ayrıca VGA renkli çıkışlar ve dikey ve yatay senkronizasyon çıkışları için "Harici Yapın".

xlconcat_0 - Blok RAM'e beslenen bir 16 bit RGB sinyali oluşturmak için ayrı renkleri birleştirir.

xlconcat_1 - VGA sürücüsünden gelen sütun ve satır sinyallerini birleştirir ve Blok RAM'in B Bağlantı Noktasına beslenir. Bu, VGA sürücüsünün piksel renk değerlerini okumasını sağlar.

VDD - Sabit YÜKSEK, Blok RAM'in yazma etkinleştirmesine bağlı, böylece her zaman doğru olabiliriz.

xlslice_0, 1, 2 - Dilimler, RGB sinyalini VGA sürücüsüne beslenebilecek ayrı R, G ve B sinyallerine bölmek için kullanılır.

Blok Tasarımı tamamlandığında, bir HDL sarmalayıcı oluşturun ve kısıtlamalar dosyasını ekleyin.

*Blok Tasarımı benlin1994 tarafından yazılan öğreticiye dayanmaktadır*

7. Adım: SDK

Bu Blok Tasarımını çalıştıran kod aşağıda yer almaktadır. Init.c, çizimi işleyen işlevleri içerir (tahminler, sayılar, derece sembolü vb.). main.c'deki ana döngü, kart programlandığında çalıştırılan şeydir. Bu döngü, tahmin ve sıcaklık değerlerini ayarlar ve ardından init.c'deki çizim işlevlerini çağırır. Şu anda yedi tahminin tümü arasında dolaşıyor ve birbiri ardına görüntüleniyor. Her görüntüyü görebilmeniz için 239 satırına bir kesme noktası eklemeniz önerilir. Kod yorumlanır ve size daha fazla bilgi verir.

Adım 8: Sonuç

Mevcut projeyi geliştirmek için, COE dosyaları biçimindeki önceden yüklenmiş tahmin görüntüleri Block Memory Generators'a yüklenebilir. Yani tahminleri C kodunda yaptığımız gibi manuel olarak çizmek yerine, resimler okunabilir. Bunu yapmaya çalıştık ama çalıştıramadık. Piksel değerlerini okuyabildik ve çıktılarını alabildik ama RAM'e yüklediklerimize hiç benzemeyen dağınık görüntüler yarattı. Block Memory Generator veri sayfasını okumak yararlıdır.

Proje, internet bağlantısı yönü eksik olduğu için esasen yarım bir Akıllı Aynadır. Bunu eklemek, eksiksiz bir Akıllı Ayna verecektir.

Önerilen:

Sonsuz Ayna Saati Yapın: 15 Adım (Resimlerle)

Sonsuz Ayna Saati Yapın: Önceki bir projede, nihai amacımın onu bir saate dönüştürmek olduğu bir sonsuzluk aynası yaptım. (Renkli Sonsuzluk Aynası Yap) Yaptıktan sonra bunun peşine düşmedim çünkü havalı görünse de onunla ilgili birkaç şey vardı

KOLAY Sonsuz Ayna Küpü Yapın - 3D Baskı YOK ve Programlama YOK: 15 Adım (Resimlerle)

KOLAY Sonsuz Ayna Küpü Yapın | 3D Baskı YOK ve Programlama YOK: Herkes iyi bir sonsuzluk küpünü sever, ancak bunları yapmak zor olacak gibi görünüyor. Bu Eğitilebilirlik için amacım, size adım adım nasıl yapılacağını göstermektir. Sadece bu değil, size verdiğim talimatlarla bir tane yapabileceksiniz

C.Q: Kendin Yap Akıllı Ayna: 5 Adım

C.Q: Kendin Yap Akıllı Ayna: Bizler WBASD STEM Academy'de ikinci sınıf öğrencileri olan Katrina Concepcion ve Adil Qaiser'iz. Bu senenin en iyi ödülü için ortaklaşa yapacağımız ve yapacağımız proje buydu. Bu projeyi yapmaya karar verdiğimizde aklımızda 'en çok e

Siyah Ayna: 4 Adım

Black Mirror: Bu proje benim akıllı ayna yapma girişimimdi. Bu projedeki amacım, aynada hala görünen bir saate sahip bir ayna yaratmaktı. Bu sayede sabah hazırlanırken tam zamanıdır. Ben de reklam vermeye çalıştım

Taşınabilir Akıllı Ayna/Makyaj Kutusu Combo Nasıl Oluşturulur: 8 Adım

Taşınabilir Akıllı Ayna/Makyaj Kutusu Kombinasyonu Nasıl Oluşturulur: Davis & Elkins kolejinde, daha büyük bir ayna ve ahududu pi kullanımı ve bir liman işlevi görecek sihirli ayna yazılım platformu ile birlikte bir makyaj seyahat kutusu tasarlamaya ve yaratmaya başladım