İçindekiler:

- Adım 1: Bir PWM Modülü Oluşturma - Kaynak Dosya

- Adım 2: Bir PWM Modülü Oluşturma - Vivado Kurulumu

- Adım 3: Bir PWM Modülü Oluşturma - Bir Proje Dosyası Oluşturma

- Adım 4: Bir PWM Modülü Oluşturma - Blok Tasarımı ve Kısıtlama Dosyası Ayarı (I)

- Adım 5: Bir PWM Modülü Oluşturma - Blok Tasarımı ve Kısıtlama Dosyası Ayarı (II)

- Adım 6: Bir PWM Modülü Oluşturma - Blok Tasarımı ve Kısıtlama Dosyası Ayarı (III)

- Adım 7: Bir PWM Modülü Oluşturma - Blok Tasarımı ve Kısıtlama Dosyası Ayarı (IV)

- Adım 8: Bir PWM Modülü Oluşturma - Blok Tasarımı ve Kısıtlama Dosyası Ayarı (V)

- Adım 9: Bir PWM Modülü Oluşturma - Donanım Kurulumu

- Adım 10: Bir PWM Modülü Oluşturma - Bit Akışı Oluşturun ve SDK'yı Başlatın

- Adım 11: Bir PWM Modülü Oluşturma - Xilinx SDK'da Yeni Bir Uygulama Oluşturma

- Adım 12: Bir PWM Modülü Oluşturma - Proje Gezgini'ne Genel Bakış (I)

- Adım 13: Bir PWM Modülü Oluşturma - Proje Gezgini'ne Genel Bakış (II)

- Adım 14: Bir PWM Modülü Oluşturma - Proje Gezgini'ne Genel Bakış (III)

- Adım 15: Bir PWM Modülü Oluşturma - PWM İşlevini (I) Toplayın

- Adım 16: Bir PWM Modülü Oluşturma - PWM İşlevini Tamamlayın (II)

- Adım 17: Bir PWM Modülü Oluşturma - PWM İşlevini Tamamlayın (III)

- Adım 18: Bir PWM Modülü Oluşturma - Çalıştırın

- Adım 19: OV7670 ile Digilent ZYBO'da Video İşleme Akışı

- Adım 20: Blok Şemasını Tamamlayın

- Adım 21: OV7670'i ZYBO'ya bağlayın

- Adım 22: Blok Tasarımı Oluşturun

- Adım 23: OV7670 Kamera Kontrolü ve Yakalama için VHDL Dosyaları Ekleyin

- Adım 24: Kısıtlama Dosyası Ekle

- Adım 25: HLS IP için IP Repo Ekleyin

- Adım 26: Modülleri ve IP'yi ekleyin

- 27. Adım: IP Yapılandırma Ayarları

- 28. Adım: PS IP Bloğu Ekleyin ve Yapılandırın

- Adım 29: Kısım 1. Servo Motorlar için bir PWM Modülü Oluşturma

- Adım 30: Video Giriş Tarafı Bağlantıları (ack Vurgulu)

- Adım 31: OV7670'e Bağlantılar

- Adım 32: Video Çıkış Tarafındaki Bağlantılar

- Adım 33: Blok ve Bağlantı Otomasyonunu Çalıştırın

- Adım 34: HDL Wrapper Oluşturun

- Adım 35: Bit Akışı Oluşturun, Donanımı SDK'ya Dışa Aktarın, SDK'yı Vivado'dan Başlatın

- Adım 36: SDK (FreeRTOS yok)

- Adım 37: FreeRTOS Uygulaması

- Adım 38: Kullanım Talimatları

- Adım 39: Referanslar ve Bağlantılar

- Yazar John Day day@howwhatproduce.com.

- Public 2024-01-30 13:21.

- Son düzenleme 2025-01-23 15:14.

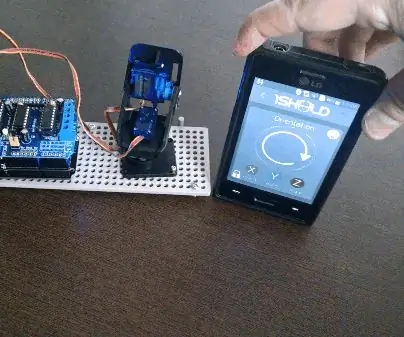

Yalnızca 2 eksenli bir servo PWM kontrol cihazı oluşturmaya ilişkin ayrıntılar için birinci adımdan başlayın.

Tüm proje için büyük blok diyagramdan (Adım 19) başlayın.

Kullandığımız kamera + Pan/tilt kurulumu:

Servoları bağlamak için Digilent'in PmodCON3'ü kullanıldı.

Adım 1: Bir PWM Modülü Oluşturma - Kaynak Dosya

Adım 2: Bir PWM Modülü Oluşturma - Vivado Kurulumu

İlk olarak, Xilinx web sitesinden Vivado Design Suite'i indirin. Vivado Yazılım Geliştirme Kiti (SDK) dahil tüm tasarım paketini kurun. Bu proje 2017.2 sürümünü kullanmaktadır.

Bu arada Digilent Adept 2 de Zybo kart sürücüsü olarak kurulmalıdır.

Adım 3: Bir PWM Modülü Oluşturma - Bir Proje Dosyası Oluşturma

Bir proje dosyası oluşturmadan önce, burada öğretici olarak Zybo dosyasını zaten düzgün bir şekilde yüklediğinizden emin olmalısınız:

Vivado Sürüm 2015.1 ve Sonrası Anakart Dosya Kurulumu

Vivado 2017.2'yi açın. Hızlı Başlangıç'ta, Proje Oluştur -> Sonraki -> Proje Adı (burada proje adınızı belirtin) -> Proje Türü'ne tıklayın. Proje Türü'nde, RTL Projesi'ni seçin ve “Şu anda kaynakları belirtme” seçeneğini işaretleyin. Ardından, Varsayılan Parça için Görünen Ad olarak “Panolar” ve “Zybo”yu seçin. Ardından, projeyi başlatmak için Bitir'e tıklayın.

Adım 4: Bir PWM Modülü Oluşturma - Blok Tasarımı ve Kısıtlama Dosyası Ayarı (I)

Flow Navigator'da “”Create Block Design” üzerine tıklayın, ardından OK'e basın. gerekli IP'leri eklemek için “+” işaretini tıklayın. Ekle:

- Bir ZYNQ7 İşleme Sistemi İki AXI Zamanlayıcı

- İki AXI Zamanlayıcı

Adım 5: Bir PWM Modülü Oluşturma - Blok Tasarımı ve Kısıtlama Dosyası Ayarı (II)

IP Ekledikten sonra Blok Otomasyonu ve bağlantı otomasyonunu çalıştırın. Otomasyon tamamlandıktan sonra “axi_timer_0” bloğunda pwm0 -> Make External üzerine sağ tıklayın. pwm0 harici pinini pwm_Xaxis olarak adlandırın. Ayrıca yukarıdaki işlemi “axi_timer_1” bloğunda tekrarlayın ve pwm0 harici pinini pwm_Zaxis olarak adlandırın.

Adım 6: Bir PWM Modülü Oluşturma - Blok Tasarımı ve Kısıtlama Dosyası Ayarı (III)

Vivado'da Blok Tasarımını her bitirdiğimizde bir HDL Wrapper oluşturmamız gerektiğine dikkat edin. Çünkü her proje için en üst düzey modül olacaktır.

Adım 7: Bir PWM Modülü Oluşturma - Blok Tasarımı ve Kısıtlama Dosyası Ayarı (IV)

Şimdi, blok diyagramımıza bağlı pinleri atamak için kısıtlama dosyamızı kurmamız gerekiyor. Blok Tasarımı penceresini kapatın, Kaynaklar sekmesinde, “Kaynak Ekle”->Kısıtlama ekle veya oluştur-> Zybo-Master.xdc'yi kısıtlama dosyalarımız olarak ekleyin.

Adım 8: Bir PWM Modülü Oluşturma - Blok Tasarımı ve Kısıtlama Dosyası Ayarı (V)

Constraints klasöründen Zybo-Master.xdc kısıtlama dosyasını açın, çıkış sinyali olarak belirtmek istediğimiz portların açıklamasını kaldırın ve XXXX'in Blok Diyagramında belirtilen harici pini ifade ettiği “get_ports{XXXX}” adını değiştirin. Kısıtlama dosyasının ayarı şekilde gösterilmiştir.

Adım 9: Bir PWM Modülü Oluşturma - Donanım Kurulumu

Servo motorları Pmod CON3'e bağlayın. TowerPro SG90 bu projede kullandığımız servo motor modelidir. Servo motor kabloları için turuncu kablo, Pmod CON3'teki SIG pinine bağlı PWM sinyalini temsil eder. Kırmızı kablo Vcc, Pmod CON3'teki VS pinine bağlı bir güç kablosudur. Son olarak, kahverengi kablo Gnd, GND pinine bağlı bir topraklama kablosudur. Ardından, Pmod CON3'ü Zybo Board'daki JD bağlantı noktasının üst sırasına yerleştirin.

Adım 10: Bir PWM Modülü Oluşturma - Bit Akışı Oluşturun ve SDK'yı Başlatın

1. Proje Gezgini sekmesinde, BitStream Oluştur'u çalıştırın.

2. Donanımı dışa aktar: Dosya > Dışa Aktar > Donanımı Dışa Aktar-> “bit akışını dahil et” seçeneğini işaretleyin-> Tamam 3. SDK'yı Başlat: Dosya -> SDK'yı Başlat.

Adım 11: Bir PWM Modülü Oluşturma - Xilinx SDK'da Yeni Bir Uygulama Oluşturma

Yeni Bir Uygulama Oluşturun:

Dosya > Yeni > Uygulama Projesi -> Projenizin adını girin -> Bitir

Proje Gezgini altında üç klasör olmalıdır.

Bu durumda, "design_1_wrapper_hw_platform_0", daha önce Vivado tarafından dışa aktarılan klasördür. Axis_2_PWM_SDK_bsp, kart destek paketi klasörüdür. Ve Axis_2_PWM_SDK, SDK'daki ana proje klasörümüzdür. “helloworld.c” dosyasını Axis_2_PWM_SDK'nın “src” klasörü altında görebilirsiniz, burada “helloworld.c” ana dosyadır.

Adım 12: Bir PWM Modülü Oluşturma - Proje Gezgini'ne Genel Bakış (I)

Proje Gezgini altındaki bazı dosyaları kontrol edelim. İlk olarak “design_1_wrapper_hw_platform_0” klasöründe “system.hdf” dosyasını açın. Bu dosya, ps7_cortex9 işlemcisinin adres haritasını ve tasarımımızda bulunan IP bloklarını gösterir.

Adım 13: Bir PWM Modülü Oluşturma - Proje Gezgini'ne Genel Bakış (II)

Ardından, “Axis_2_PWM_SDK_bsp” klasörü altındaki “include” ve “libsrc” dosyasını kontrol edin. Buradaki kitaplık dosyaları, kayıt "oynatmadan" donanım çevre birimleriyle etkileşime girmemizi sağlar.

Adım 14: Bir PWM Modülü Oluşturma - Proje Gezgini'ne Genel Bakış (III)

BSP belgeleri aracılığıyla xtmrctr.h, AXI Zamanlayıcı ile ilgili bir Xilinx Zamanlayıcı Kontrol Kitaplığı olarak bulunur. Tipik olarak, istenen PWM işlevini burada bulabiliriz. Ancak, “tmrctr_v4_3” belgesini okursanız, sürücünün şu anda cihazın PWM çalışmasını desteklemediğini gösterir. PWM fonksiyonundaki eksiklikten dolayı xtmrctr.h ve AXI Timer v2.0 LogiCORE IP Product Guide yardımıyla PWM fonksiyonumuzu tamamlamamız gerekiyor.

Adım 15: Bir PWM Modülü Oluşturma - PWM İşlevini (I) Toplayın

“helloworld.c” ana dosyasına geri dönün, aşağıdaki başlık dosyalarını ekleyin:

Adım 16: Bir PWM Modülü Oluşturma - PWM İşlevini Tamamlayın (II)

“xparameters.h” aracılığıyla iki AXI TIMER'ın temel adreslerini tanımlayın.

Adım 17: Bir PWM Modülü Oluşturma - PWM İşlevini Tamamlayın (III)

İstenen PWM işlevini oluşturun.

Duty_val: derece değerini görev döngüsüne dönüştürür. PWM_Freq_Duty: PWM oluşturmak için istenen frekansı ve görev döngüsünü ayarlayın. Saat periyodu da atanmalıdır.

PWM_START: PWM kayıt adresini atayın ve PWM oluşturmaya başlayın.

PWM_STOP: PWM kayıt adresini atayın ve PWM üretmeyi durdurun.

Demo kodunun geri kalanı "helloworld.c"de "Axis_2_PWM_SDK" altında gösterilir.

Adım 18: Bir PWM Modülü Oluşturma - Çalıştırın

1. FPGA'yı SDK aracılığıyla programlayın

- Zybo Board'u USB portu üzerinden PC'ye bağlayın.

- Xilinx Araçları -> FPGA Programı

2. Programı çalıştırın

“Çalıştır” simgesine tıklayın ve menüyü aşağı indirin -> Farklı Çalıştır -> Donanımda Başlat

3. SDK Terminali

- SDK Terminalini Açın -> Seri Bağlantı Noktasına Bağlan -> Tamam

- Programı çalıştır. Demo kodu başarılı bir şekilde çalışırsa, “Başlatma tamamlandı!” ifadesini görmelisiniz. SDK Terminalinde.

Adım 19: OV7670 ile Digilent ZYBO'da Video İşleme Akışı

Ekli tam arşiv dosyası.

Adım 20: Blok Şemasını Tamamlayın

Bu, projedeki tüm bağlantıların ve IP bloklarının tam şemasını gösterir.

Adım 21: OV7670'i ZYBO'ya bağlayın

ov7670 modülünü ZYBO Pmod'lara bağlamak için bir bağlantı oluşturun

Veri Pmod, Pmod D'dir

Kontrol Pmod, Pmod C'dir

Ek olarak, bu öğreticinin ilk yarısında belirtildiği gibi PmodCON3 ve servoları bağlayın

Adım 22: Blok Tasarımı Oluşturun

Akış Gezgini'nde "Blok Tasarımı Oluştur"a tıklayın, ardından Tamam'a basın.

Adım 23: OV7670 Kamera Kontrolü ve Yakalama için VHDL Dosyaları Ekleyin

Bu adıma eklenen VHDL dosyalarını projeye ekleyin

Adım 24: Kısıtlama Dosyası Ekle

Ekli kısıtlamalar dosyasını projenize ekleyin.

Adım 25: HLS IP için IP Repo Ekleyin

Ekli Zip dosyasını alın ve "HLS_repo" adlı yeni bir dizinde (klasör) benzer şekilde adlandırılan yeni bir klasöre açın.

IP kataloğuna giderek projenize bir IP deposu ekleyin ve "Depo Ekle…" öğesini seçerek sağ tıklayın.

"HLS_repo" dizininize gidin ve onu seçin.

İsteğe bağlı: HLS video işleme bloğunu kendiniz oluşturun!

Adım 26: Modülleri ve IP'yi ekleyin

ov7670_axi_stream_capture, debounce ve ov7670_controller modüllerini arka plana sağ tıklayıp "Modül Ekle…" seçeneğini seçerek blok şemasına ekleyin.

Benzer şekilde, IP'leri ekleyin:

- HLS_Video_Track

- Video Çerçevesi Arabelleği Yazma

- Video Çerçevesi Tampon Okuması

- Video Zamanlama denetleyicisi

- AXI4-Video Çıkışına Akış

- 3 "Dilim"

- Devamlı

- 2 AXI Zamanlayıcı

27. Adım: IP Yapılandırma Ayarları

Resimlerde gösterildiği gibi

28. Adım: PS IP Bloğu Ekleyin ve Yapılandırın

ZYNQ7 İşleme Sistemini blok diyagrama ekleyin

yapılandırmayı düzenleyin:

-

PS-PL yapılandırması

-

HP

- S HP 0'ı Etkinleştir

- S HP 1'i Etkinleştir

-

-

Saat yapılandırması

-

PL Kumaş Saatler

- 100MHz'de FCLK_0

- 25 MHz'de FCLK_1 (OutputClock)

- FLCK_2, 35MHz'de (<=50MHz) (CameraClock)

-

Adım 29: Kısım 1. Servo Motorlar için bir PWM Modülü Oluşturma

axi_timer_0 pwm0'ı yeni çıkış portu pwm_Xaxis'e getirin

axi_timer_1 pwm0'ı yeni çıkış bağlantı noktası pwm_Zaxis'e getirin

Adım 30: Video Giriş Tarafı Bağlantıları (ack Vurgulu)

Video giriş tarafı IP bloklarını doğru şekilde bağlayın

(* bu bağlantılar, bağlantı otomasyonu sırasında doğru seçenekler seçilerek oluşturulmalıdır) axi_stream_capture'dan "aclk" şuraya gider:

- ap_clk video karesi arabelleğinde yazma

- HLS video akışı işleme bloğunda ap_clk

- *Video Çerçevesi Arabelleğinden AXI smartconnect IP'sine aclk S_AXI_HP0'a yazın

- *aclk, HLS video işleme bloğunun S_AXI kanalları için AXI Interconnect IP'sinin kanallarına karşılık gelir ve video çerçeve arabelleği PS bloğuna S_AXI_HP0_ACLK yazar

Video akışı sinyali, yakalama bloğundan Zynq bellek arayüzüne seri olarak bağlanır.

- Video, yakalama bloğundan HLS işleme bloğuna gider.

- HLS bloğundan işlenen video, çerçeve arabelleği yazma bloğuna gider.

- *Çerçeve arabelleği yazma bloğu, Zynq PS bloğundaki HP0 arabirimine bağlanır.

- Yakalama bloğunun çıkışından gelen m_axis_tuser sinyali, hem HLS işleme bloğu üzerindeki video_in_TUSER giriş sinyaline hem de aynı blok üzerindeki ap_start sinyaline manuel olarak bağlanır.

TUSER(tuser) sinyali, videonun bir karesinin başlangıcını belirtmek için AXI video akışı protokolü tarafından kullanılır. AP_Start, HLS bloğuna işlemeye başlamasını söyler. Bu nedenle, her kareyi olduğu gibi işlemek için HLS bloğunu tetiklemek için tuser kullanıyoruz. gelir. Bir veri yolunun tek bir sinyalini bağlarken ve bu şekilde bölerken, onu veri yolunun geri kalanının normal sonlandırma noktasına da bağlamak gerekir. Vivado, sinyali manuel olarak bağlarsanız, normalde bağlanacağı şeyin bağlantısını kesmek istediğinizi varsayar.

IP bloklarının yapılandırma ayarları:

Video kare arabelleği yazma:

Video formatları: RGB8

Saat başına 1 örnek Maks. sütunlar: 1280 (>=640) Maks. satırlar: 960 (>=480) Maks. veri genişliği: 8

Adım 31: OV7670'e Bağlantılar

ov7670_axi_stream_capture bloğunda

- Tüm girişleri harici yapın (bir pime sağ tıklayın ve menüden seçin veya sol tıklama->ctrl+T)

- İsimleri olduğu gibi bırakın

ov7670_controller bloğunda

- Tüm blok çıkışlarını harici yap

- config_finished bağlantı noktasını led0 olarak yeniden adlandırın

- clk'yi CameraClock'a bağlayın (<=50MHz) (FCLK_2)

Geri dönme bloğunda

- button1 girişini btn0 adlı harici bir giriş bağlantı noktasına bağlayın

- out1'i ov7670_controller IP bloğundaki yeniden gönderme hattına bağlayın

- button2 girişini btn3 adlı harici bir giriş bağlantı noktasına bağlayın

- out2n'yi video yakalama saati etki alanı için İşlemci Sistem Sıfırlama IP'sindeki ext_reset_in girişine bağlayın. (*Bu IP oluşturulduktan sonra yapılması gerekebilir*)

- clk'yi CameraClock'a bağlayın (<=50MHz) (FCLK_2)

Adım 32: Video Çıkış Tarafındaki Bağlantılar

Blok Video Zamanlama Denetleyicisi (VTC), AXI4-Video Çıkışına Akış ve dilimler için bağlantılar

- vid_io_out_clk ve VTC clk için 25 MHz saat (FCLK_1) kullanın

- AXI4-Stream to Video Out üzerinde aclk için 100MHz saat (FCLK_0) kullanın

- vtiming_out'tan vtiming_in'e

- Video Çerçevesi Arabelleği Okuma m_axis_video, AXI4-Video Çıkışına Akış video_in'e gider

- vtg_ce gen_clken'e gider

- VTC clken, aclken, vid_io_out_ce'yi Sabit doout[0:0] ile bağla

- vid_hsync ve vid_vsync'i sırasıyla vga_hs ve vga_vs harici çıkış bağlantı noktalarına getirin. (resimde değil)

dilimler:

-

Dilimler ekteki resimlerde gösterildiği gibi ayarlanmalıdır.

- blokları dilim_kırmızı, dilim_yeşil ve dilim_mavi olarak yeniden adlandırın

- blok adına göre resimlerde gösterildiği gibi dilim aralıklarını ayarlayın

- resimde gösterildiği gibi her dilim çıkışını harici bir bağlantı noktası çıkışına bağlayın.

- vid_data[23:0] her dilim için girişlere bağlanır (Din[23:0])

Adım 33: Blok ve Bağlantı Otomasyonunu Çalıştırın

ZYNQ7 PS bloğundaki şeyleri bağlamak için Block Automation'ı çalıştırın. Resimde gösterildiği gibi.

Tüm ara bağlantı IP'lerini oluşturmak için Bağlantı otomasyonunu çalıştırın. Her resimdeki tüm seçeneklere çok dikkat edin.

Geri dönme bloğunda, out2n'yi video yakalama saati etki alanı İşlemci Sistem Sıfırlaması ext_reset_in girişine bağlayın.

Adım 34: HDL Wrapper Oluşturun

Blok tasarımınız için HDL Wrapper oluşturun.

En üst modül olarak ayarlayın.

Adım 35: Bit Akışı Oluşturun, Donanımı SDK'ya Dışa Aktarın, SDK'yı Vivado'dan Başlatın

Dışa aktarma işlemine bit akışını eklediğinizden emin olun.

Bit akışının oluşturulması çok uzun zaman alabilir.

Ardından SDK'yı başlatın

Adım 36: SDK (FreeRTOS yok)

Bu sürüm, FreeRTOS kullanmadan her şeyi yapar ve kodu güzel bir şekilde yoğunlaştırır.

Donanım tasarımına dayalı bağımsız bir BSP oluşturun. Varsayılan seçenekler iyi olmalıdır. BSP kaynaklarının oluşturulduğundan emin olun.

Resimde gösterildiği gibi Uygulama oluşturun. (boş uygulama)

Otomatik oluşturulan ana dosyayı silin ve ekli dosyaları içe aktarın.

Adım 37: FreeRTOS Uygulaması

Bu sürüm, FreeRTOS kullanır. Donanım tasarımına dayalı bir FreeRTOS901 BSP oluşturun. Varsayılan seçenekler iyi olmalıdır. BSP kaynaklarının oluşturulduğundan emin olun.

Resimde gösterildiği gibi Uygulama oluşturun. (boş uygulama)

Otomatik oluşturulan ana dosyayı silin ve ekli dosyaları içe aktarın.

Adım 38: Kullanım Talimatları

Bu projeyi yürütmek biraz zor. Adımları sırasıyla takip edin.

ZYBO'nuzun açıldığında hiçbir şeyi kendi kendine yüklemediğinden emin olun. Bu, Bitti LED'inin yanmaması gerektiği anlamına gelir. Bunu yapmanın bir yolu, önyükleme kaynağı atlama telini JTAG'a ayarlamaktır.

Programlamak istediğiniz projeyi (FreeRTOS veya değil) SDK'dan açın

- ZYBO'nuzu açın. Bitti LED'i yanmamalıdır.

- FPGA'yı bit dosyası ile programlayın. Bitti LED'i yanmalıdır. Led0 yanmamalıdır.

- Kodu çalıştırın (bunu yapıyorsanız başlangıç kesme noktasını geçmeyi unutmayın).

Bu noktada VGA ekranınızda bir çıktı alıyor olmalısınız.

Yeniden başlatmak için (hata veya herhangi bir şey olursa): hızlıca PS-SRST düğmesine dokunun veya ZYBO'yu kapatıp tekrar açın. 2. adımdan devam edin.

İşlemciyi hata ayıklayıcıyla durdurmak, Kameranın hareket etmek yerine konumunu korumasına neden olur. Video akışı yine de devam edecek.

Adım 39: Referanslar ve Bağlantılar

Xilinx başvuru kılavuzları ve belgeleri:

- PG044 - Video Çıkışına AXI Akışı

- PG278 - Video Çerçevesi Arabelleği Okuma/Yazma

Diğer bağlantılar:

- Lauri'nin blogu - VDMA girişi

- Lauri'nin blogu - BRAM kullanarak OV7670 - VGA çıkışı

- Hamsterworks wiki, Mike Fields tarafından, OV7670 kodunun orijinal kaynağı

- Temel zamanlama özelliklerini gösteren veri sayfası

Önerilen:

Cep Telefonu Kontrollü Pan Tilt: 4 Adım

Cep Telefonu ile Kontrol Edilen Pan Tilt: Herkese Merhaba, Bu yeni projemde sizlere Cep Telefonu ile kontrol edilen bir Pan-Tilt'i tanıtacağım. Cep telefonunun tüm hareketleri pan-tilt cihazında Bluetooth aracılığıyla yeniden üretiliyor. Yapısı çok Arduino R3 (veya benzeri) kullanarak basit ve tw

DSLR Zaman Atlamaları için Pan ve Tilt Mekanizması: 7 Adım (Resimlerle)

DSLR Zaman Atlamaları için Kaydırma ve Eğme Mekanizması: Etrafta duran birkaç step motorum vardı ve gerçekten onları havalı bir şeyler yapmak için kullanmak istedim. DSLR fotoğraf makinem için harika zaman aralıkları yaratabilmek için bir Pan ve Tilt sistemi yapmaya karar verdim. İhtiyacınız olacak ürünler: 2 adet step motor -htt

IOT123 - SOLAR TRACKER - TILT/PAN, PANEL FRAME, LDR MOUNTS RIG: 9 Adım (Resimlerle)

IOT123 - SOLAR TRACKER - TILT/PAN, PANEL ÇERÇEVE, LDR MOUNTS RIG: Çift eksenli güneş izleyicileri için kendin yap tasarımlarının çoğu "dışarıda"; Birkaç Güneş Pili, mikro denetleyici, pil ve muhafaza etrafında itmek için gerçekten düşük dereceli 9G Mikro Servo'ya dayanmaktadır. Etrafında tasarlayabilirsiniz

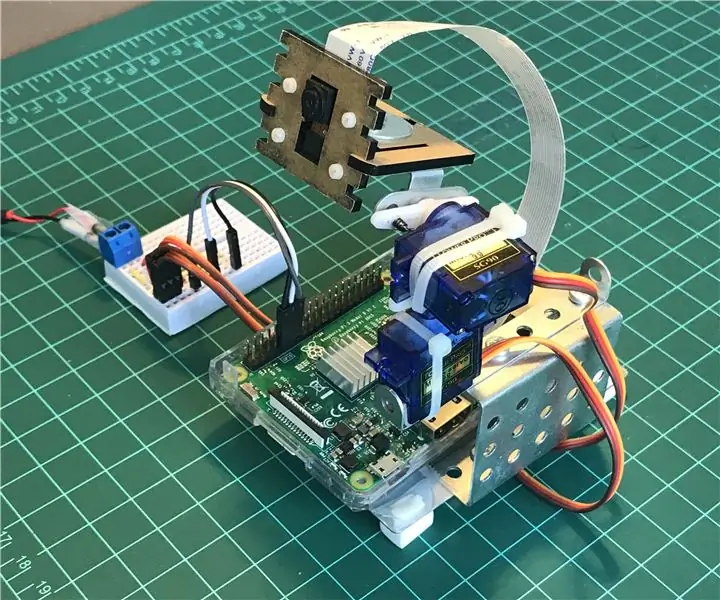

Pan-Tilt Multi Servo Kontrol: 11 Adım (Resimlerle)

Pan-Tilt Çoklu Servo Kontrolü: Bu eğitimde, bir Raspberry Pi üzerinde Python kullanarak çoklu servoların nasıl kontrol edileceğini keşfedeceğiz. Amacımız bir kamerayı (bir PiCam) konumlandırmak için bir PAN/TILT mekanizması olacak. Burada nihai projemizin nasıl çalışacağını görebilirsiniz: Kontrol Servo Kontrol döngü testi:

Uzaktan Kumandalı Pan ve Tilt Başlığı: 7 Adım

Uzaktan Kumandalı Pan ve Tilt Kafası: Her zaman uzaktan kumandalı bir pan ve tilt kafası istemişimdir. Belki video kameram, lastik bant atıcı veya su tabancası nişancısı içindi. Bu küçük proje ile üst güverteye ne koyduğunuz gerçekten önemli değil (çok ağır olmadığı sürece),